基于VerilogHDL的FIR數(shù)字濾波器設(shè)計(jì)與仿真

1、設(shè)計(jì)意圖

本文引用地址:http://www.104case.com/article/267699.htm本例主要是在Stratix 器件內(nèi)實(shí)現(xiàn)基本有限脈沖響應(yīng)濾波器。

FIR 的基本結(jié)構(gòu)包括一系列的乘法和加法。FIR 的運(yùn)算可用式( 1) 的方程描述, 現(xiàn)重寫如下:

x(n)表示輸入樣本序列, h(n)代表濾波器的系數(shù), L 是抽頭的數(shù)量。

一個(gè)L=8 的FIR 設(shè)計(jì)如圖2, 利用了輸入的8 個(gè)樣本。因此稱之為8 抽頭濾波器。該結(jié)構(gòu)是有一個(gè)移位寄存器, 乘法器和加法器組成的, 可實(shí)現(xiàn)L=8 階的FIR。其數(shù)據(jù)通道必須足夠?qū)? 以適應(yīng)乘法器和加法器的輸出。這些采樣值被編碼為有限

字長(zhǎng)的形式, 然后通過(guò)M個(gè)寄存器并行移動(dòng)。可見(jiàn)用一個(gè)MAC級(jí)連鏈就可以構(gòu)成這種機(jī)器。每個(gè)寄存器提供一個(gè)單位樣本內(nèi)延遲。這些延遲輸入與各自的系數(shù)相乘, 然后疊加得到輸出。圖2 所示為基于MAC 的8 階FIR 數(shù)字濾波器結(jié)構(gòu)。

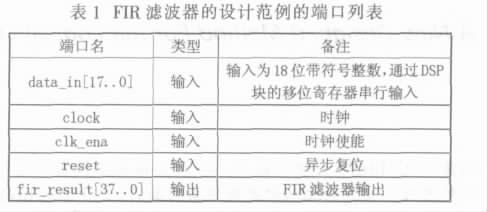

在該設(shè)計(jì)中有八個(gè)抽頭, 各抽頭有18 位輸入和濾波器系數(shù)。由于一個(gè)DSP 塊可以支持4 個(gè)18 位輸入的分支, 所以設(shè)計(jì)需要2 個(gè)DSP 塊。輸入數(shù)據(jù)串行加載到DSP 塊中, DSP 內(nèi)部的移入/移出寄存器鏈用于產(chǎn)生延遲。濾波器系數(shù)從TriMatrix(tm)的ROM存儲(chǔ)器中加載。

2、Verilog HDL 代碼編寫風(fēng)格

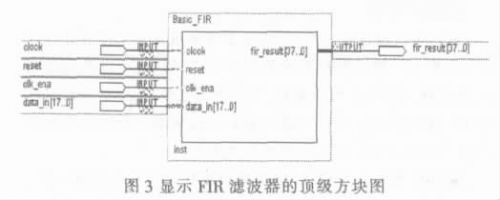

HDL 代碼編寫應(yīng)該具有很好的易讀性和可重用性, 而自頂向下的分割方法可以幫助我們達(dá)到最佳的結(jié)果。HDL 代碼在達(dá)到功能的情況下要盡可能的簡(jiǎn)潔, 盡量避免使用帶有特殊庫(kù)單元的實(shí)例, 因?yàn)檫@樣會(huì)使得整個(gè)進(jìn)程變得不可靠。在本設(shè)計(jì)中, 我們將設(shè)計(jì)劃分成一個(gè)頂級(jí)文件和三個(gè)次級(jí)文件, 并且調(diào)用了QuartusII 中的MegaFunction 功能輔助完成整個(gè)設(shè)計(jì)。

3、驗(yàn)證仿真

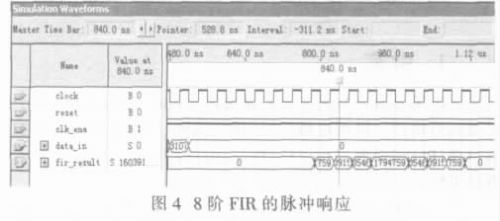

完全可綜合設(shè)計(jì)的一個(gè)優(yōu)點(diǎn)就是同樣的HDL 代碼能夠用于驗(yàn)證和綜合。在使用HDL 代碼之前必須要驗(yàn)證設(shè)計(jì)的功能,最好且最簡(jiǎn)單的方法就是利用驗(yàn)證工具, 其次是利用仿真工具作有目的的仿真。QuartusII 內(nèi)部帶有仿真器, 只要通過(guò)建立正確的Vector Waveform File( 向量波形文件) 就可以開(kāi)始仿真了。圖4 所示為QuartusII 內(nèi)部仿真器得到的8 階FIR 的脈沖響應(yīng)波形。

3 結(jié)論

利用Verilog HDL 設(shè)計(jì)數(shù)字濾波器的最大優(yōu)點(diǎn)就是可使設(shè)計(jì)更加靈活。比較硬件電路圖設(shè)計(jì), Verilog HDL 語(yǔ)言設(shè)計(jì)的參數(shù)可以很容易在Verilog 程序中更改, 通過(guò)綜合工具的簡(jiǎn)化和綜合即可以得到電路圖, 其效率要高出利用卡諾圖進(jìn)行人工設(shè)計(jì)許多。而且編譯過(guò)程也非常簡(jiǎn)單高效。優(yōu)秀編碼風(fēng)格能夠在綜合過(guò)程中節(jié)省芯片使用的單元, 從而降低設(shè)計(jì)成本。

濾波器相關(guān)文章:濾波器原理

濾波器相關(guān)文章:濾波器原理

低通濾波器相關(guān)文章:低通濾波器原理

電源濾波器相關(guān)文章:電源濾波器原理

數(shù)字濾波器相關(guān)文章:數(shù)字濾波器原理 鎖相環(huán)相關(guān)文章:鎖相環(huán)原理

評(píng)論