基于IP核的FIR低通濾波器的設(shè)計(jì)與實(shí)現(xiàn)

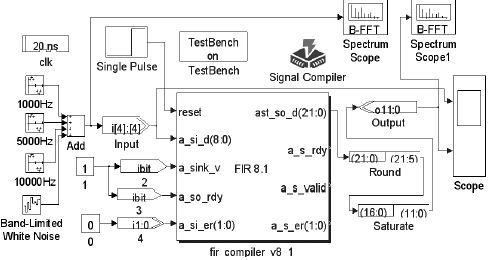

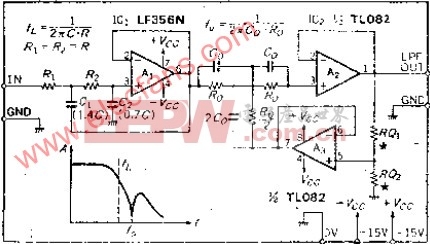

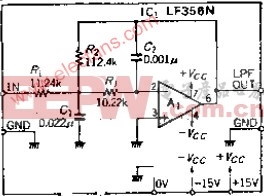

調(diào)用FIR 濾波器IP 核以及DSP Builder 中的相關(guān)元件,構(gòu)建了FIR低通濾波器的仿真模型,如圖2 所示。如圖2 所示,輸入信號(hào)頻率為200Hz、1000Hz、2000Hz 正弦波和寬帶白噪聲疊加而成的信號(hào)。

本文引用地址:http://www.104case.com/article/267693.htm

圖2 FIR濾波器仿真模型

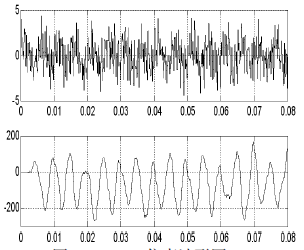

圖3 Simulink 仿真波形圖

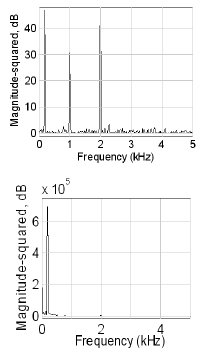

仿真以后,此信號(hào)經(jīng)過截止頻率為500Hz 的低通濾波器濾波以后,1000Hz 和2000Hz 的高頻正弦波均被較好的濾除了。濾波前后的時(shí)域波形圖如圖3 所示。圖4 是濾波前后信號(hào)的頻譜圖。可以看出,此16階的濾波器濾波性能符合要求。

圖4 濾波前后頻譜圖

3.結(jié)果分析

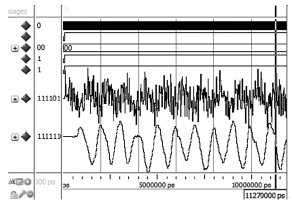

圖5 FIR低通濾波器RTL仿真波形

仿真通過以后,再運(yùn)行Signal Compiler 將此模型轉(zhuǎn)換成RTL 寄存器傳輸級(jí)的VHDL 硬件描述語言。再用Modelsim 軟件進(jìn)行寄存器傳輸級(jí)仿真。仿真結(jié)果如圖5 所示。

可以看出,經(jīng)過對(duì)轉(zhuǎn)換后的VHDL 語言進(jìn)行時(shí)序仿真,濾波效果良好,進(jìn)一步驗(yàn)證了模型的正確性。在此基礎(chǔ)上,調(diào)用QuartusII 軟件進(jìn)行邏輯綜合與適配,最終在Cyclone II 系列EP2C35F672C8 芯片上獲得了最高響應(yīng)速度為151.88MHz 的高速FIR 低通濾波器。資源使用情況:邏輯單元1347 /33216(4%),全部組合邏輯872/33216(3%),專業(yè)邏輯寄存器1231/33216(4%),引腳29 /475(6%),總存儲(chǔ)位41160/483840(9%)。

4.結(jié)論

FIR 濾波器的設(shè)計(jì)與FPGA 高速實(shí)現(xiàn)一直是信號(hào)處理領(lǐng)域研究的熱點(diǎn),本文利用FIR 有限沖擊響應(yīng)濾波器IP 核,設(shè)計(jì)了截止頻率為500Hz 的FIR 低通濾波器,在Simulink 中建立了仿真模型并進(jìn)行了仿真。最終在EP2C35F672C8 型號(hào)FPGA 上得到了最高響應(yīng)頻率為151.88MHz 的高速FIR 低通濾波器。設(shè)計(jì)效率和濾波器性能得到了極大的提高。

濾波器相關(guān)文章:濾波器原理

濾波器相關(guān)文章:濾波器原理

低通濾波器相關(guān)文章:低通濾波器原理

電源濾波器相關(guān)文章:電源濾波器原理

數(shù)字濾波器相關(guān)文章:數(shù)字濾波器原理

評(píng)論