X波段基片集成波導(dǎo)帶通濾波器的設(shè)計(jì)

2 設(shè)計(jì)實(shí)例

本文引用地址:http://www.104case.com/article/267442.htm2.1 基片集成波導(dǎo)與微帶過(guò)渡的設(shè)計(jì)

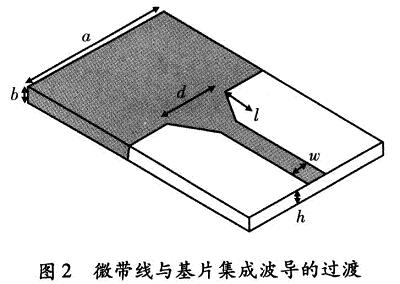

測(cè)試基片集成波導(dǎo)器件既不能利用傳統(tǒng)測(cè)試金屬波導(dǎo)的實(shí)驗(yàn)裝置,也不能利用測(cè)試微波毫米波平面電路的實(shí)驗(yàn)裝置。文中利用基片集成波導(dǎo)易與其他微波平面電路集成的特點(diǎn),采用微帶漸進(jìn)線,如圖2所示,實(shí)現(xiàn)基片集成波導(dǎo)與50 Ω微帶線的過(guò)渡,通過(guò)50 Ω微帶線實(shí)現(xiàn)對(duì)基片集成波導(dǎo)濾波器的測(cè)試。經(jīng)HFSS 10仿真優(yōu)化后,得到如下的過(guò)渡尺寸:l=4 mm,w=0.64 mm,d=1.8 mm。

2.2 基片集成波導(dǎo)濾波器的設(shè)計(jì)

文中設(shè)計(jì)的基片集成波導(dǎo)帶通濾波器參數(shù)如下:濾波器的中心頻率是9.5 GHz,通帶9.1~9.9 GHz(相對(duì)帶寬8.42%),通帶內(nèi)允許有0.5 dB的波紋,阻帶頻率分別是8.3 GHz和10.7 GHz,阻帶上的最小衰減是40 dB。該濾波器采用9階切比雪夫并聯(lián)電感耦合波導(dǎo)濾波器結(jié)構(gòu),介質(zhì)基片選用高介電常數(shù)基片CER_10(介電常數(shù)是9.5,厚度是0.63 mm)。選用高介電常數(shù)基片一方面可以有效地減小基片集成波導(dǎo)濾波器的尺寸,另一方面由于高介電常數(shù)基片的損耗正切相對(duì)較大,也會(huì)增加基片集成波導(dǎo)濾波器的插入損耗。

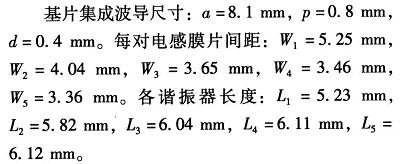

X波段基片集成波導(dǎo)濾波器尺寸如下:

2.3 仿真分析

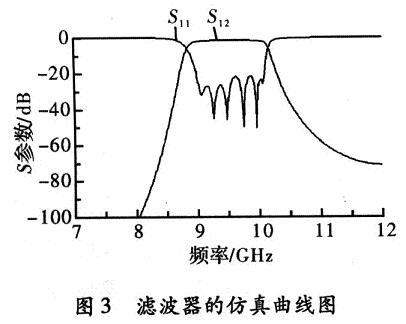

運(yùn)用HFSS 10仿真,結(jié)果如圖3所示。

由仿真結(jié)果可知,該濾波器的中心頻率是9.5 GHz,帶寬是1 GHz,通帶內(nèi)插入損耗是1.9 dB,回波損耗<一20 dB。在阻帶頻率是8.3 GHz和10.7 GHz的阻帶上,阻帶衰減>50 dB。

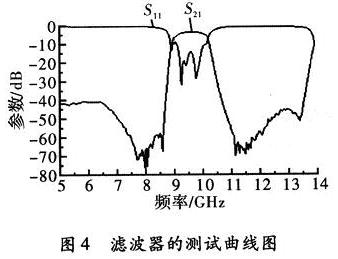

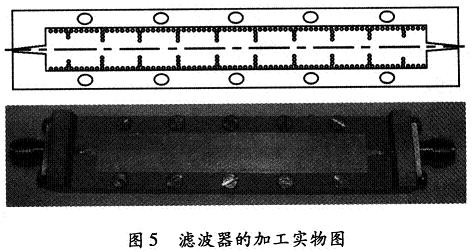

利用惠普8510矢量網(wǎng)絡(luò)分析儀進(jìn)行測(cè)試,實(shí)測(cè)結(jié)果,如圖4所示。由實(shí)測(cè)結(jié)果可知,該濾波器的中心頻率是9.58 GHz,帶寬是800 MHz,通帶內(nèi)插入損耗是3.8 dB,紋波是0.2 dB,回波損耗<一15 dB,在阻帶頻率是8.3 GHz和10.7 GHz的地方,阻帶衰減>44 dB。實(shí)測(cè)插入損耗偏高是因?yàn)閷?shí)測(cè)插入損耗除了濾波器本身的損耗外還包括一對(duì)SMA接頭的損耗和微帶漸變線過(guò)渡的損耗。實(shí)測(cè)中心頻率向高頻段漂移了80 MHz,帶寬減小了200 MHz,主要是由基片的介電常數(shù)不穩(wěn)定造成的。在頻率是14 GHz的地方出現(xiàn)寄生通帶是基片集成波導(dǎo)中的高次模相互作用的結(jié)果,可以通過(guò)調(diào)整諧振器的長(zhǎng)度使寄生通帶遠(yuǎn)離濾波器通帶。加工實(shí)物,如圖5所示。

3 結(jié)束語(yǔ)

文中利用基片集成波導(dǎo)結(jié)構(gòu)設(shè)計(jì)并制作出了一種X波段中心頻率是9.58 GHz、相對(duì)帶寬是8.35%的9階切比雪夫并聯(lián)電感耦合波導(dǎo)帶通濾波器。該濾波器在9.18~9.98 GHz的通帶范圍內(nèi)表現(xiàn)出了良好的性能。要想獲得更理想的結(jié)果,除了保證仿真模型和測(cè)試方法的準(zhǔn)確外,更需要進(jìn)一步提高加工精度,減小加工誤差。

濾波器相關(guān)文章:濾波器原理

漏電保護(hù)器相關(guān)文章:漏電保護(hù)器原理

dc相關(guān)文章:dc是什么

濾波器相關(guān)文章:濾波器原理

電源濾波器相關(guān)文章:電源濾波器原理

晶振相關(guān)文章:晶振原理 漏電開關(guān)相關(guān)文章:漏電開關(guān)原理 漏電保護(hù)開關(guān)相關(guān)文章:漏電保護(hù)開關(guān)原理 數(shù)字濾波器相關(guān)文章:數(shù)字濾波器原理

評(píng)論