二階有源帶通濾波器原理圖及設計流程

本文為您帶來二階有源帶通濾波器設計具體流程,帶通濾波器原理圖電路圖含義、帶通濾波器方案選擇、仿真,電路性能測試,直流穩壓電源設計、運放及電壓跟隨器選擇。

本文引用地址:http://www.104case.com/article/201710/368833.htm什么是帶通濾波器?

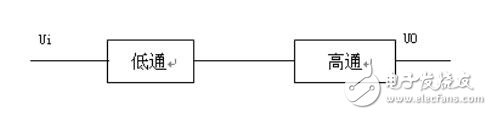

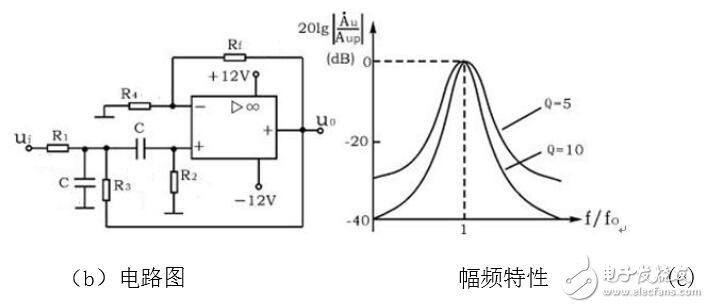

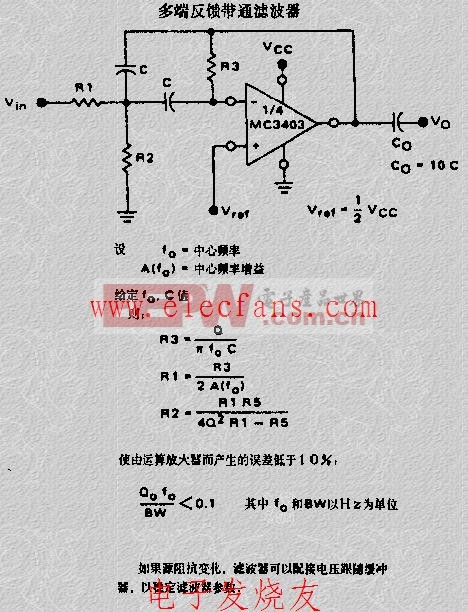

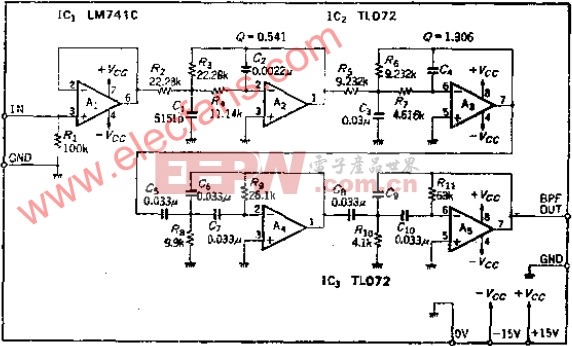

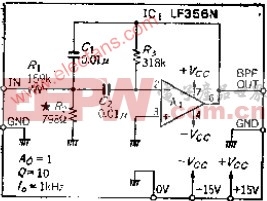

帶通濾波器是指只允許在某一個通頻帶范圍內的信號通過的濾波器,而比通頻帶下限頻率低和比上限頻率高的信號均加以衰減或抑制,注意:要將高通的下限截止頻率設置為小于低通的上限截止頻率。反之則為帶阻濾波器。典型的帶通濾波器可以從二階低通濾波器中將其中一級改成高通而成。如圖2-4所示。

(a) 帶通濾波器原理框圖

圖2-4 二階帶通濾波器

帶通濾波器電路性能、參數:

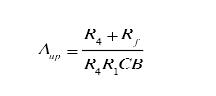

通帶增益Aup:

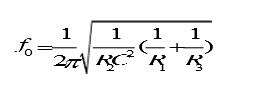

中心頻率0f:

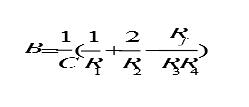

通帶寬度B:

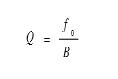

品質因素Q:

此電路的優點是改變R和R4的比例就可改變頻寬而不影響中心頻率。

有源帶通濾波器的設計要求指標

1.帶寬要求:15Hz~35KHz

2.帶外抑制比要求:>=-20dB/倍頻程

方案的選擇及流程

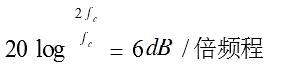

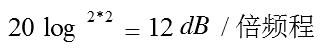

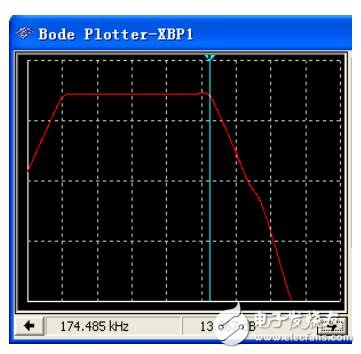

1.階數的選擇根據所需帶外抑制比大于等于20dB/倍頻程,我們選用了四階帶通濾波器,因為選用二階時為:

選用三階時為:

選用四階時為:

此時可以滿足要求帶外抑制比≥20dB/倍頻程

倍頻程和10倍頻程的選擇:

對于濾波或運放放大倍數來講是用dB來表示的。具體的公式是

A(w)=A0/(1+jw/w0),w0是濾波頻率或運放的一個極點。

采用dB表示時是 20*log|A(w)|. A(w) 要取模,即A0/sqrt(1+w*w/(w0*w0)).

對于n倍頻(靠近w0的頻率不準確,n>0),w2=n*w1, w1>>w0.(開方中的1可忽略)則有:

A(w2)-A(w1) = 20*logA0-20*log(sqrt(w2*w2)/(w0*w0)) -20*logA0+20*log(sqrt(w1*w1)/(w0*w0))

= -10*log(w2*w2/(w1*w1) = -10*log(n*n)

這樣對于兩倍頻,w2=2*w1,則此時下降是 -10*log4=-6.02dB 當w2=10*w1時 -10*log100=-20dB.

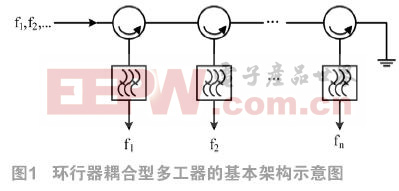

2.電路形式的選擇由于我們所選的濾波器階數n為偶數,所以我們選用n/2個二階濾波器級聯;

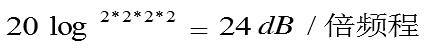

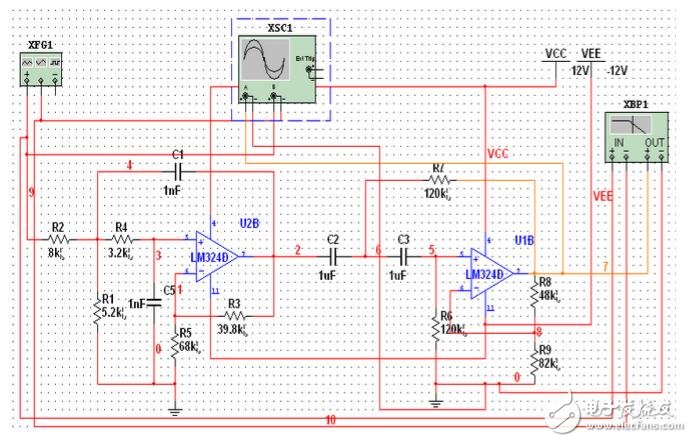

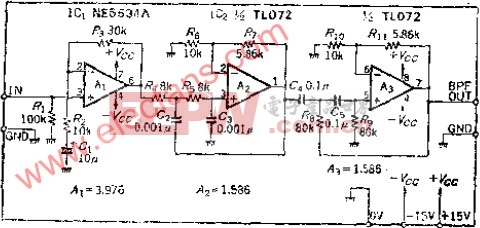

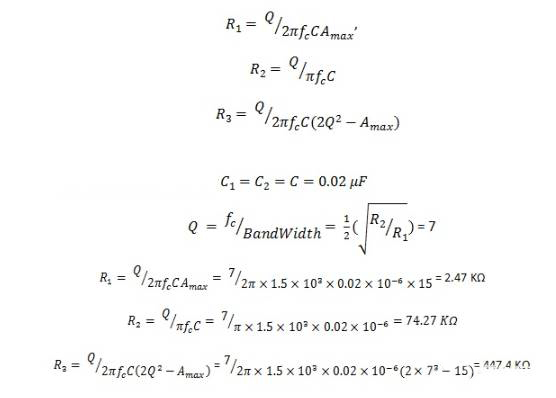

3.原理圖仿真依原理圖用MulTIsim 10.0進行仿真,使基本達標。我們用Protel99SE畫出來的設計原理圖:

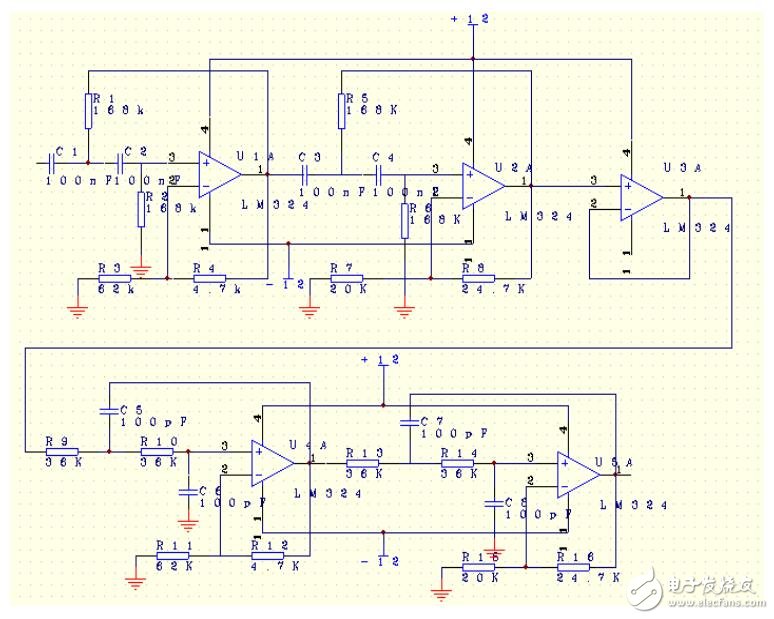

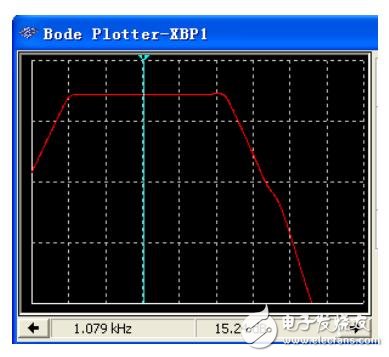

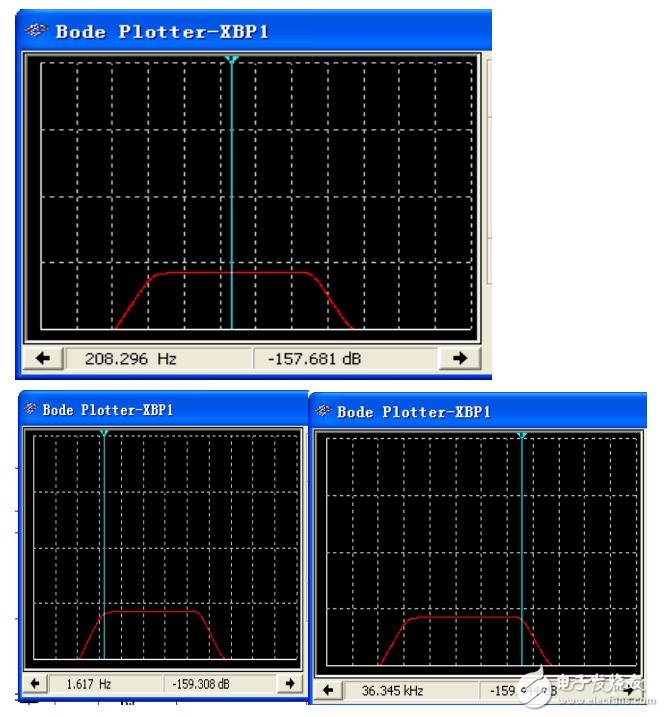

下面是我們的仿真結果:

這幅圖是我們在MulTIsim 10.0進行仿真時得到的波特圖,其中給定

R9 = R10 = 8.2K

R13 = R14 = 8.2K

R4 = R12 = 4.7K

其它參數值如圖所示,這也是我們組前期仿真過程中遺留下來的最不可原諒并且是最最核心的問題,在后面會對它做進一步說明。

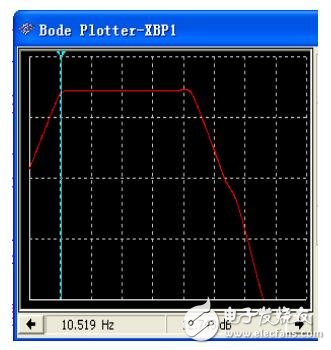

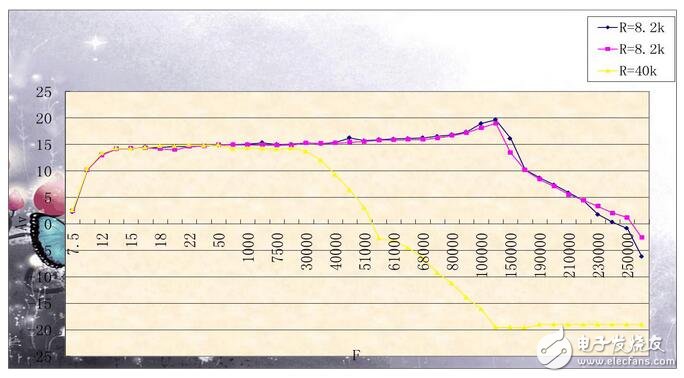

下面是我們的仿真結果:

可以看到仿真出來的帶寬已經非常寬了,上限頻率很高,這與我們的初始仿真結果出現了很大的偏差。(初始仿真結果為:10.225Hz~61.743KHz)。

電路性能測試和改進

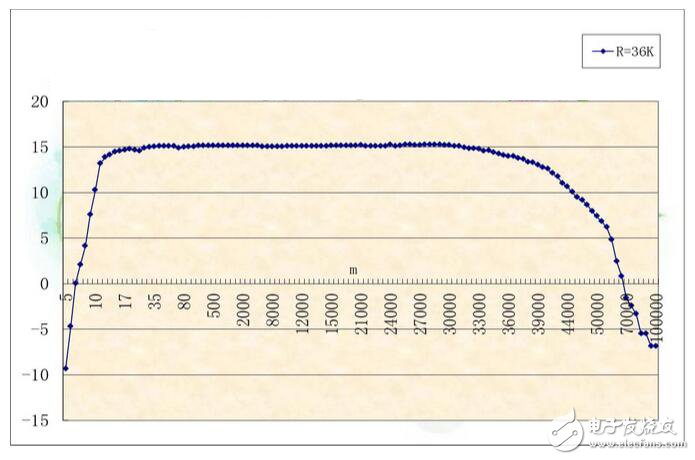

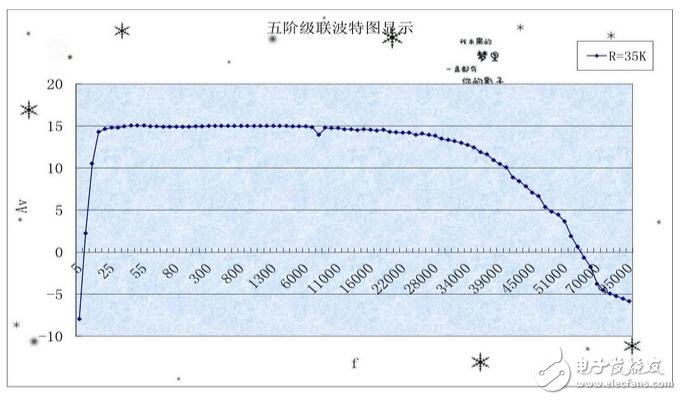

做出來的電路先出現了峰值:

電阻出了問題,改變阻值后:

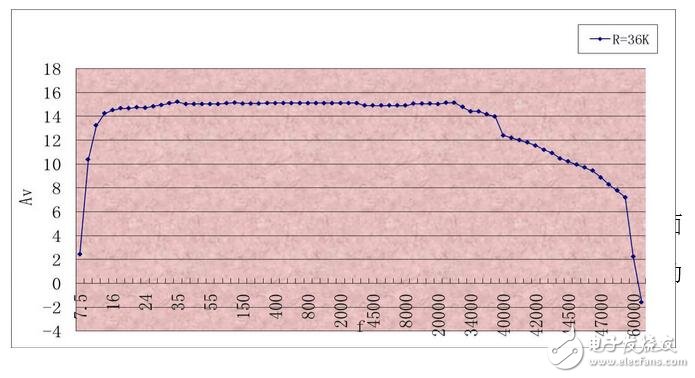

再次改變阻值后:

帶外抑制比不夠:

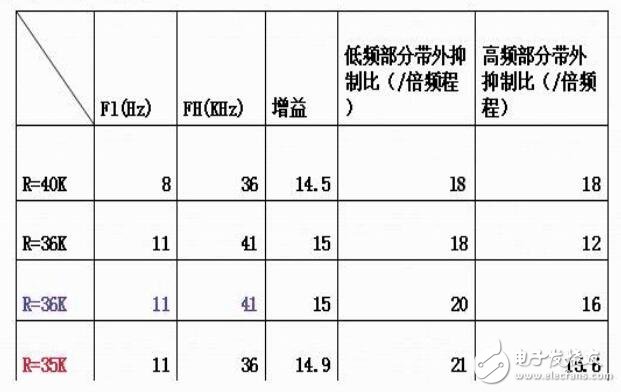

相關數據表

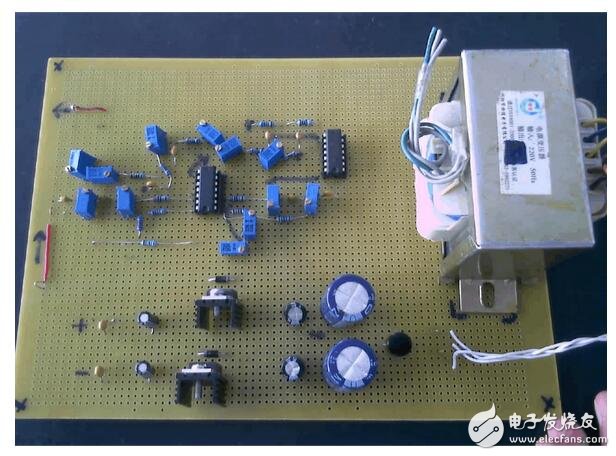

由此可以看出R的取值為40k或36k時,條件基本滿足條件。下面所示是我在萬能板上實際焊接出來的實物圖:

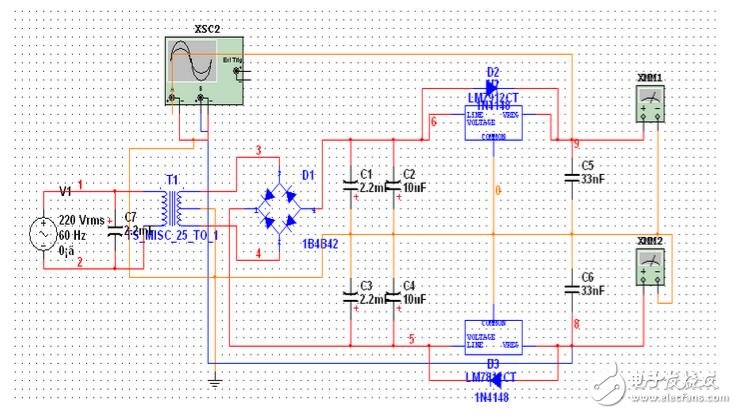

電源模塊:

直流穩壓電源的工作原理

電源是構成一個完整功放的重要組成部分,其穩定的向外電路提供能量,保證外電路能正常的進行工作。但一般地都是從市電經變壓器降壓而實現的,那么如何降壓,如何把交流經某些元件變成直流,并保證其能穩定的輸出是必須考慮的問題。

做為穩壓電源它是由電源變壓器、整流、濾波和穩壓電路等四部分組成。電源變壓器是將交流電網220v的電壓變為所需要的電壓值,然后通過整流電路將交流電壓變成脈動的直流電壓。而脈動的直流電壓含有較大的紋波,必須通過濾波電路加以消除,從而得到平滑的直流電壓。

A .變壓器

變壓器的種類有許多,單輸出的雙輸出的,體型有大有小,輸出電壓、功率等依型號而定。外電路所需電壓值、流過電源的電流、外電路的功率都將影響到電源輸出電壓的穩定性,因此輸出電壓、本身功率等都是必須考慮的,在本電路中我們選擇雙12v輸出電壓的變壓器。

B .整流電路

要使交流電壓變成直流電壓,整流電路就是必須的。常見的整流電路有單相半波整流、單相全波整流、單相橋式整流和倍壓整流電路。由于橋式整流電路輸出電壓高,紋波電壓較小,管子所承受的最大反向電壓較低,同時因電源變壓器在正、負半周內都有電流供給負載,電源 變壓器得到了充分的利用,效率較高。因此我們在此采用最大電流2A的整流橋。

C .濾波電路

濾波電路用于濾去整流輸出電壓中的紋波,一般由電抗元件組成。其工作機理是,點抗性元件在電路中有儲能作用,并聯的電容器C在電源供給的電壓升高時,能把部分能量儲有平波的作用。電感也有平波的作用,使負載電壓比較平滑。電容濾波一般針對小功率電源,而電感濾波多用于大功率電源中。此電路中我們采用電容濾波方式。電容濾波時輸出電壓為U2=√2U1,其中U1為變壓器輸出電壓,U2 為電容兩端輸出電壓。

由于該電路采用雙電源形式,我們將采取上下并聯兩組電容的形式來作為濾波電路。并且電容由大到小依次排列。第二級電容采用鉭電解電容有效地防止了低頻干擾成分對電路的干擾, 第三極電容采用獨石電容防止了高頻成分的干擾,同時也提高了電源的穩定性。

電源部分采用三端集成穩壓塊LM7812和LM7912制作,電路結構簡單,電路中芯片所需電壓為±12V,實際測得電壓為11.86V和11.74V。我們在具體測量的時候選用此電源模塊。

運放的選擇

為了減少運放對濾波電路的負載效應,同時便于調整,我們剛開 始考慮選用LF412。這是一種具有JFET作為輸入級的低失調、高輸入阻抗運放。其輸入阻抗可達1210Ω。單位帶寬增益積為8MHz,能滿足我們的要求,但因為此芯片大多為軍用芯片,價位太高,所以我們選用了LM324,因為LM324系列器件為價格便宜的帶有真差動輸入的四運算放大器。與單電源應用場合的標準運算放大器相比,它們有一些顯著優點。該四放大器可以工作在低到3.0伏或者高到32伏的電源下,靜態電流為MC1741的靜態電流的五分之一。共模輸入范圍包括負電源,因而消除了在許多應用場合中采用外部偏置元件的必要性。3dB帶寬增益乘積:1.2MHz ,低功耗,已經可以滿足我們的要求了。

電壓跟隨器

概括地講,電壓跟隨器起緩沖、隔離、提高帶載能力的作用。共集電路的輸入高阻抗,輸出低阻抗的特性,使得它在電路中可以起到阻抗匹配的作用,能夠使得后一級的放大電路更好的工作。電壓隔離器輸出電壓近似輸入電壓幅度,并對前級電路呈高阻狀態,對后級電路呈低阻狀態,因而對前后級電路起到“隔離”作用。電壓跟隨器常用作中間級,以“隔離”前后級之間的影響,此時稱之為緩沖級。基本原理還是利用它的輸入阻抗高和輸出阻抗低之特點。電壓跟隨器的輸入阻抗高、輸出阻抗低特點,可以極端一點去理解,當輸入阻抗很高時,就相當于對前級電路開路;當輸出阻抗很低時,對后級電路就相當于一個恒壓源,即輸出電壓不受后級電路阻抗影響。一個對前級電路相當于開路,輸出電壓又不受后級阻抗影響的電路當然具備隔離作用,即使前、后級電路之間互不影響。

利用電壓跟隨器的這些特點,我們在電路高低銅連接處增加了電壓跟隨器模塊,是的電路性能大幅度優化,主要表現在通帶內的平坦程度得以提升,帶寬也有所增加。

存在問題解決情況

⑴ 濾波器的構架的選擇在剛開始的原理建立及電路構架的確立時,我們也曾想過用兩個二階Delyiannis帶通濾波器級聯,也就是下面圖中給出來的那樣:

下面給出仿真得到的波特圖:

由上圖可以看到,當帶寬可基本達標時,增益都到-157dB了,雖然我們的設計指標中沒有增益限制,但我們不可能這么大倍數的衰減新號,所以我們放棄這種設計方案,轉而采取高通與低通級聯的方式,選用二階Salley-key濾波電路為基礎模塊設計濾波器電路,在前面已做過重點說明,這里不再重復。

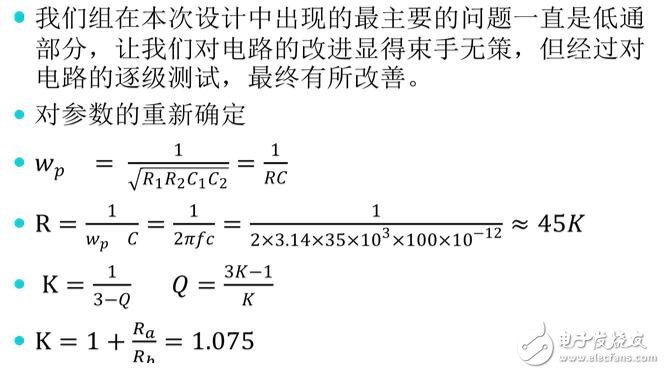

(2) 低通部分的改進由于在仿真階段的疏忽和調節的盲目,使得地同參數出了很大問題,一直到實際電路搭接出來后還在為低通電路部分發愁。后來通過對仿真圖的調節、實際電路的分塊測試,低通濾波電路的不可行之處實實在在的擺在我們眼前,因此重新開始從計算開始,確立參數,在上面已經予以說明,但新的問題又出現了,高頻部分波特圖出現轉折,且轉折前后斜率不盡相同,在之前給出的方針和實測圖中都有反映出來,其原因初步被判定為是兩個二階濾波電路頻率不匹配,致使濾波通帶沒有能完全重合。

(3) 電源問題

我們的第二個電源出了一些問題,也耽誤了很長時間,測量數據為:正電源11.6V、負電源為-22V.整流橋測過沒出問題,電路都是通的,穩壓塊也換過,但一直沒能解決,問題還是出在穩壓塊上,應該是被燒掉了。

(4) 帶外抑制比

思路一:帶外抑制比在比較精確的一組測量是幾乎為20db,具體的思路是:由于電路是級聯的,在高通部分他的帶外抑制比比較高,但是第通的部分相應的低些,這時可以在他的低通部分在增加一個極點,使得在該點處他的下降先變化一次,這樣就比較的陡了。

思路二:在電路設計的時候,我才用的電容比值太大了,達到了1000倍,這個可能是一個原因,導致帶外衰減部分比較的低,此后我想過改變容值的方法來減小他們之間的系數,這樣就可以使得他們的靈敏度減小,電路性能得到改善。

評論