如何在FPGA中實(shí)現(xiàn)狀態(tài)機(jī)

實(shí)現(xiàn)狀態(tài)機(jī)

本文引用地址:http://www.104case.com/article/266770.htm使用VHDL這樣的高級(jí)語言,可以輕松地直接從狀態(tài)圖實(shí)現(xiàn)狀態(tài)機(jī)。VHDL支持多種枚舉類型,方便您定義實(shí)際的狀態(tài)名稱。舉例如下:

TYPE state IS (idle, led_on, led_off) ;

上面的類型定義對(duì)應(yīng)的是圖1中所示的狀態(tài)圖,即用于在按下按鈕時(shí)切換發(fā)光二極管開/關(guān)的狀態(tài)機(jī)。

實(shí)現(xiàn)狀態(tài)機(jī)有許多種方法,可分為兩類基本方法。第一類基本方法就是一次性將所有內(nèi)容集成到單個(gè)進(jìn)程中。第二類基本方法是雙進(jìn)程法,將組合邏輯和順序邏輯分開。

一般來說,大多數(shù)工程師都傾向于實(shí)現(xiàn)單進(jìn)程狀態(tài)機(jī)。與傳統(tǒng)上講授的雙進(jìn)程法相比,這種方法具有以下優(yōu)勢:

可以避免組合過程中信號(hào)覆蓋不完全造成的閉鎖風(fēng)險(xiǎn)。

狀態(tài)機(jī)的輸出與時(shí)鐘保持同步。

通常比雙進(jìn)程實(shí)現(xiàn)方案更容易調(diào)試。

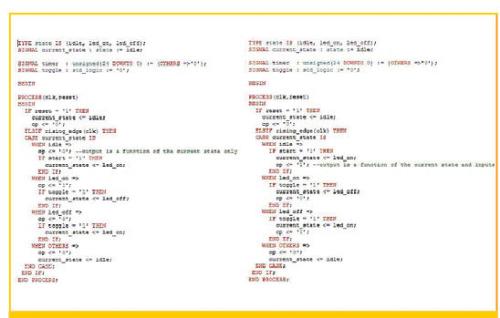

無論您決定采用哪一種方法來實(shí)現(xiàn)狀態(tài)機(jī),都需要使用CASE語句來評(píng)估下一狀態(tài)的判定和任何輸出,如圖4所示。該圖并行比較了使用單進(jìn)程法的Moore狀態(tài)機(jī)(左)和Mealy狀態(tài)機(jī)(右)。

圖4,使用VHDL語言的Moore狀態(tài)機(jī)(左)和Mealy狀態(tài)機(jī)。

狀態(tài)機(jī)編碼

狀態(tài)變量存儲(chǔ)在觸發(fā)器中,使用下一時(shí)鐘邊緣上的下一狀態(tài)進(jìn)行更新(即使沒有狀態(tài)變化也是如此)。如何使用觸發(fā)器來表示狀態(tài)值具體取決于狀態(tài)的數(shù)量和是否選擇用某種特定的方法來管理綜合工具。狀態(tài)編碼最常見的三種類型是:

順序碼--狀態(tài)編碼遵循傳統(tǒng)的狀態(tài)二進(jìn)制序列。

格雷碼--除了狀態(tài)編碼使用格雷碼,且狀態(tài)編碼串之間只有一個(gè)位變化外,其它基本與順序編碼方法類似。

獨(dú)熱碼--這種方法在狀態(tài)機(jī)中為每一種狀態(tài)分配一個(gè)觸發(fā)器。只有一個(gè)觸發(fā)器當(dāng)前設(shè)置為高位,其余均設(shè)置為低位。故稱為“獨(dú)熱”.

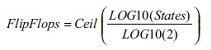

順序編碼和格雷編碼都需要一定數(shù)量的觸發(fā)器,可以通過下列等式來確定:

相比之下,獨(dú)熱編碼法所需的觸發(fā)器數(shù)量和狀態(tài)數(shù)量一樣多。

狀態(tài)編碼的自動(dòng)分配取決于狀態(tài)機(jī)所包含的狀態(tài)數(shù)量。同時(shí)還需要考慮您選擇使用的綜合工具。您可以根據(jù)下列經(jīng)驗(yàn)法則來選取編碼方法:

順序:少于5種狀態(tài)。

獨(dú)熱:5-50種狀態(tài)。

格雷:多于50種狀態(tài)。

一般情況下您不必去考慮使用哪一種狀態(tài)編碼方法,而是讓綜合引擎工具確定合適的實(shí)現(xiàn)方案,只在選擇的方法出現(xiàn)問題時(shí)進(jìn)行考慮。但是,如果您要全盤自 行掌控,并定義狀態(tài)編碼方法,也沒必要手動(dòng)操作,只需使用狀態(tài)編碼為每一種狀態(tài)設(shè)定常數(shù)即可。相反地,可以使用代碼中的一個(gè)屬性來驅(qū)動(dòng)綜合工具,從而選擇 特定的編碼方法。具體如下所示:

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_encoding STRING;

ATTRIBUTE syn_encoding OF current_state :

SIGNAL IS “sequential”;

其中“sequential”也可以是“gray”和“onehot”.您還可以通過結(jié)合使用“safe”屬性來確保在狀態(tài)機(jī)進(jìn)入非法狀態(tài)時(shí)能夠恢復(fù)到有效狀態(tài)。

另外,您也可以使用syn_encoding屬性直接定義狀態(tài)編碼的值。例如,假設(shè)您想要使用下列狀態(tài)編碼法來對(duì)三態(tài)狀態(tài)機(jī)進(jìn)行編碼:Idle = “11,”led_on = “10,” led_off = “01(與較傳統(tǒng)的順序”00“、”01“和”10“不同):

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_encoding STRING;

ATTRIBUTE syn_encoding OF current_state :

SIGNAL IS ”sequential“;

工程師負(fù)責(zé)在綜合工具中使用正確的設(shè)置,以確保該工具不會(huì)忽略任何屬性。例如,賽靈思XST工具要求將FSM選項(xiàng)設(shè)置為USER,而Synopsys的Synplify則要求關(guān)閉FSM編譯器。

前面給出的等式可確定狀態(tài)機(jī)實(shí)現(xiàn)方案所需的觸發(fā)器數(shù)量。由于不是所有的狀態(tài)機(jī)都是2的冪次方,因此某些狀態(tài)在設(shè)計(jì)中將不會(huì)用到。實(shí)現(xiàn)狀態(tài)機(jī)的工程師 必須負(fù)責(zé)確保未使用的狀態(tài)在設(shè)計(jì)中得到妥善處理。可以采用幾種適用于多種設(shè)計(jì)的基本技巧來實(shí)現(xiàn)這一目標(biāo)。對(duì)于高度可靠的安全關(guān)鍵型設(shè)計(jì),則需要采用其它更 高級(jí)的技巧。

不過對(duì)于大多數(shù)應(yīng)用來說,只需要確保狀態(tài)機(jī)能夠妥善地處理未使用的狀態(tài)并在進(jìn)入非法狀態(tài)時(shí)能夠正確地恢復(fù)。要做到這一點(diǎn)有兩種主要的方法。第一種方 法是使用綜合工具實(shí)現(xiàn)一個(gè)安全的狀態(tài)機(jī)。綜合工具通常會(huì)插入額外的邏輯,用于檢測非法狀態(tài)并將狀態(tài)機(jī)返回到有效狀態(tài)。第二種方法是加強(qiáng)對(duì)實(shí)現(xiàn)邏輯的控制, 聲明所有2的冪次方狀態(tài)機(jī)的狀態(tài),并使用另一屬性來確保即便是在沒有入口條件下,2的冪次方狀態(tài)機(jī)的狀態(tài)也不會(huì)被優(yōu)化掉。這意味著除非出錯(cuò)(單粒子翻轉(zhuǎn) 等),狀態(tài)機(jī)內(nèi)部的任何條件都不會(huì)進(jìn)入狀態(tài)。下面的代碼顯示了通過使用屬性以防止清除未使用的狀態(tài)。

TYPE state IS (idle, led_on, led_off) ;

SIGNAL current_state : state := idle;

ATTRIBUTE syn_keep BOOLEAN;

ATTRIBUTE syn_keep OF current_state :

SIGNAL IS TRUE”;

簡而言之,安全高效的狀態(tài)機(jī)設(shè)計(jì)對(duì)于任何使用FPGA的工程師而言都是一項(xiàng)重要技能。選擇Moore狀態(tài)機(jī)、Mealy狀態(tài)機(jī)還是混合機(jī)取決于整個(gè)系統(tǒng)的需求。無論選擇哪種類型的狀態(tài)機(jī),充分掌握實(shí)現(xiàn)方案所需的工具和技巧,將確保您實(shí)現(xiàn)最佳解決方案。

fpga相關(guān)文章:fpga是什么

塵埃粒子計(jì)數(shù)器相關(guān)文章:塵埃粒子計(jì)數(shù)器原理

評(píng)論