硬件電路時序計算方法與應用實例

其中,狀態(tài)類信號是單端LVTTL信號,接收端利用TSCLK的上升沿對TSTAT[1:0]采樣,方向為從物理層芯片發(fā)往鏈路層芯片;數(shù)據(jù)類信號是差分LVDS信號,接收端利用TDCLK的上升沿與下降沿對TDAT[15:0]和TCTL采樣,即一個時鐘周期進行兩次采樣,方向為從鏈路層芯片發(fā)往物理層芯片。

本文引用地址:http://www.104case.com/article/266060.htm由于接收信號組與發(fā)送信號組的時序分析類似,因此本文僅對發(fā)送信號組進行時序分析。

在本設(shè)計中,采用Vitesee公司的VSC9128作為鏈路層芯片,VSC7323作為物理層芯片,以下參數(shù)分別從這兩個芯片的Datasheet中提取出來。

● 狀態(tài)類信號的時序分析

對狀態(tài)類信號,信號的流向是從物理層芯片發(fā)送到鏈路層芯片。

第一步,確定信號工作頻率,對狀態(tài)類信號,本設(shè)計設(shè)定其工作頻率和時鐘周期為:

Freq=78.125MHz;

Tcycle = 1/ Freq = 12.8ns;

第二步,從發(fā)送端,即物理層芯片手冊提取以下參數(shù)[3]:

-1ns < Tco < 2.5ns;

第三步,從接收端,即鏈路層芯片手冊提取建立時間和保持時間的要求[4]:

Tsetup(min) = 2ns;

Thold(min) = 0.5ns;

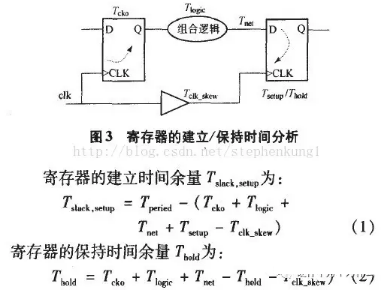

將以上數(shù)據(jù)代入式1和式2:

2.5ns + (Tflight-data - T flight-clk)MAX + 2ns < 12.8ns

-1ns + (Tflight-data - T flight-clk)MIN > 0.5ns 整理得到:

1.5ns < (Tflight-data - T flight-clk) < 8.3ns

基于以上結(jié)論,同時考慮到Vsig = 6inch/ns,可以得到如下結(jié)論,當數(shù)據(jù)信號和時鐘信號走線長度關(guān)系滿足以下關(guān)系時,狀態(tài)類信號的時序要求將得到滿足:TSTAT信號走線長度比TSCLK長9英寸,但最多不能超過49.8英寸。

● 數(shù)據(jù)類信號的時序分析

對數(shù)據(jù)類信號,信號的流向是從鏈路層芯片發(fā)送到物理層芯片。

第一步,確定信號工作頻率,對數(shù)據(jù)類信號,本設(shè)計設(shè)定其工作頻率為:

Freq=414.72MHz;

與狀態(tài)類信號不同的是,數(shù)據(jù)類信號是雙邊沿采樣,即,一個時鐘周期對應兩次采樣,因此采樣周期為時鐘周期的一半。采樣周期計算方法為:

Tsample = ½*Tcycle = 1.2ns;

第二步,從發(fā)送端,即鏈路層芯片手冊提取以下參數(shù)[4]:

-0.28ns < Tco < 0.28ns;

第三步,從接收端,即物理層芯片資料可以提取如下需求[3]:

Tsetup(min) = 0.17ns;

Thold(min) = 0.21ns;

將以上數(shù)據(jù)代入式1和式2,需特別注意的是,對數(shù)據(jù)類信號,由于是雙邊沿采樣,應采用Tsample代替式1中的Tcycle:

0.28ns + (Tflight-data - T flight-clk)MAX + 0.17ns < 1.2ns

-0.28ns + (Tflight-data - T flight-clk)MIN > 0.21ns

整理得到:

0.49ns < (Tflight-data - T flight-clk) < 0.75ns

基于以上結(jié)論,同時考慮到Vsig = 6inch/ns,可以得到如下結(jié)論,當數(shù)據(jù)信號和時鐘信號走線長度關(guān)系滿足以下關(guān)系時,數(shù)據(jù)類信號的時序要求將得到滿足:TDAT、TCTL信號走線長度比TDCLK長2.94英寸,但最多不能超過4.5英寸。

5 結(jié)論

高速電路中的時序設(shè)計,雖然看似復雜,然而只要明晰其分析方法,問題可以迎刃而解。

參考文獻:

[1] 王劍宇. 高速電路設(shè)計實踐[M]. 電子工業(yè)出版社,2010:131

[2] Optical Internetworking Forum. Implementation Agreement: OIF-SPI4-02.0[J]. OIF,2002:1-5

[3] Vitesse. VSC7323 Datasheet[J]. Vitesse,2006: 306~312

[4] Vitesse. VSC9125 and VSC9128 Datasheet[J]. Vitesse,2006:769-772

評論