利用FPGA實現的FFT變換設計

隨著集成電路的飛速發展,在圖像處理,通信和多媒體等很多領域中,數字信號處理技術已經被廣泛應用。快速傅立葉變換(FFT)算法的提出,使得數字信號處理的運算時間上面縮短了好幾個數量級。因此對FFT算法及其實現方法的研究具有很強的理論和現實意義。

本文引用地址:http://www.104case.com/article/266000.htm1 FFT算法及其實現方法

現場可編程門陣列FPGA是一種可編程使用的信號處理器件,其運算速度高,內置高速乘法器可實現復雜累加乘法運算;同時其存儲量大,無需外接存儲器就可實現大量數據運算;而且算法實現簡單,通過VHDL編程語言可輕松實現功能開發,縮短了開發周期。FPGA已經在通訊、視頻、圖像處理等領域被廣泛使用。

本次設計采用FPGA實現8點32位的FFT變換,現場可編程門陣列FPGA是一種可編程使用的信號處理器件,用戶可以通過改變配置信息對其功能進行定義,以滿足設計需求。與DSP相比,FPGA實現FFT具有速度高,存儲容量大,硬件實現簡單,I/O帶寬高等特點。

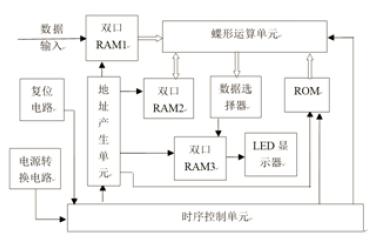

FFT處理器被分成一下幾個主要的功能模塊:數據地址產生單元、蝶形運算單元、數據選擇單元、控制單元、存儲單元等。通過VHDL語言在CycloneII系列芯片上編程實現。運算方案采用順序處理的方法。傅立葉變換實現時首先進行基2、基4分解,一般來說,如果算法使用基2實現,雖然使用的資源較多,但速度優勢明顯。設計中采用基-2DIT-FFT算法來實現整個系統的設計,如圖1所示。

圖1

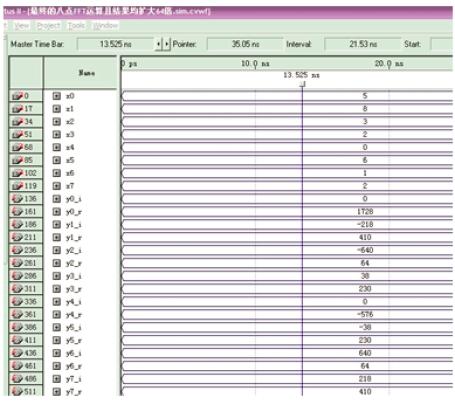

在FFT模塊的設計中,旋轉因子與輸入數據進行的是一個小數乘法的蝶形運算,需要將旋轉因子表示成小數的二進制形式。為了保證運算結果的正確性,還需要將輸入和輸出數據進行小數點的調整。在此次設計中采用定點小數的方法,所謂定點小數,就是小數點的位置是固定的。設計中統一將小數點放在了Q6的位置,在仿真的結果圖中顯示的輸出數據均是小數點經過移位后的結果即結果均擴大了64倍。

復數乘法器采用FPGA內部IP核的例化與調用來設計實現了蝶形處理,這樣就可以提高蝶形運算單元的的運算速度,降低了運算復雜度。控制單元的設計通過一個有限狀態機來實現控制器。通過有限狀態機狀態的輸出分別控制ROM因子表、隨機存儲器RAM和蝶形處理器。使它們可以協調一致地工作,從而實現FFT運算的正確輸出。

將系統設計的各個模塊連接起來,利用順序處理的FFT設計結構,將輸入數據的8個點放到RAM中進行處理。經過元件例化和調用操作完一級蝶形之后對其結果進行存儲;之后完成二級蝶形操作及存儲;最后進行三級蝶形的操作。

若輸入8點數據為[5,8,3,2.0,6,1,2].其仿真結果經轉換后的值為(即結果擴大了64倍):[1728,410-j218,64-j640,230+j38,-576,230-j38,64+j640,410+j218 ],與MATLAB仿真的結果一致。

如圖2所示,圖中的x0,x1,x2……x7是輸入信號,分別給它們輸入的值為[5,8,3,2,0,6,1,2];y0_i,y0_r……y7_i,y7_r是仿真中得到的輸出信號。經過運算,輸出結果與理論計算結果一致。

圖2

2總結

通過仿真驗證此次利用FPGA實現的FFT設計采用內置雙端口RAM、ROM單元,實現了存取數據、旋轉因子計算、蝶形計算,系統結構簡單,運算可靠性高,速度得到了進一步提升。

評論