一種節能型可升級異步FIFO的FPGA實現

2.1 FIFO空/滿信號的產生

本文引用地址:http://www.104case.com/article/265945.htm在異步FIFO的設計中,空/滿信號的產生是其主要的難點。當寫入數據時,寫信號指針追上讀信號指針的情況,意味著FIFO滿的狀態。同理在讀出數據時,讀地址指針追上寫地址指針的情況,意味著FIFO為空狀態。以上的分析可以得出,不能簡單通過讀地址指針等于寫地址指針來判定FIFO的空/滿狀態。有效的解決方法在文獻[1]、文獻[2]中都被采用。若FIFO的深度為N,則其讀/寫地址指針的寬度應為log2(N)位,讀/寫地址指針都增加一位,變為log2(N)+1位后,測試讀地址指針與寫地址指針,當兩者相等時,FIFO即為空狀態。而當FIFO讀地址指針與寫地址指針的最高有效位不同而其他有效位完全相同時,即為FIFO滿狀態,這種循環的地址指針即是環型FIFO的由來。在本文的設計中,空/滿信號不僅用于指示FIFO的狀態,還用于讀/寫時鐘的控制,從而達到節能的目地。

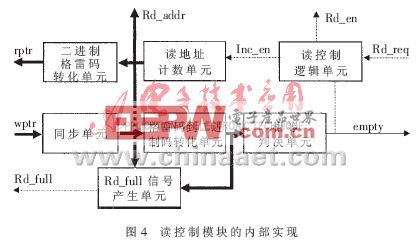

2.2 讀控制模塊

讀數據控制模塊主要功能是:根據數據的輸出及讀請求信號產生用于讀數據的控制信號、讀地址指針、FIFO空(empty)信號以及用于控制寫時鐘Wr_full信號(其具體功用在2.3中介紹)。當外部有數據讀出請求(Rd_req有效)且FIFO不為空時,使能FIFO的讀有效,FIFO輸出數據,輸出數據完成后讀地址指針加1。其中空信號的產生采用2.1中的方法,其內部實現的具體框圖如圖4所示。

在圖4中,讀控制邏輯單元主要用于產生讀使能信號,依據讀請求信號和FIFO的空(empty)信號產生讀使能。當有讀請求并且FIFO不為空時,讀使能有效,同時使地址指針加1。讀地址計數器即是一個二進制的計數器,產生輸入雙口RAM的讀地址指針。由于讀地址指針要傳輸到寫控制模塊,而兩模塊處于不同的時鐘域,為了使數據有效傳輸到寫時鐘域,采用先將讀地址指針表示的二進制數轉化為格雷碼(具體實現參見文獻[2])后再傳輸。

2.2.1 同步模塊的實現

由于實際應用于系統中時鐘頻率較高,為了達到穩定,選擇了流水線的同步器單元。在圖2的基礎上增加寄存器的位寬。為了使系統的穩定性增強,采用三級流水線的結構,當然,也可以根據自己實際的需要而增減流水線級數。

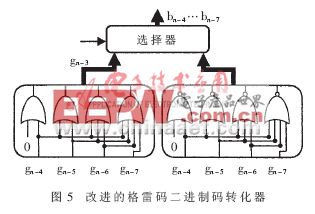

2.2.2 格雷碼二進制碼轉化

為了應用環型指針區別FIFO的空/滿信號,需要將傳輸過來用格雷碼表示的寫地址指針轉化為二進制碼,格雷碼到二進制碼轉化的公式如式(1)。設格雷碼表示的數據與二進制碼有n位,格雷碼表示為:gn-1gn-2…g0,相應二進制碼表示為:bn-1bn-2…b0。轉化公式為:

式(1)中所示的加代表無進位的加法,實現中使用“異或門”即可。但是,完全按照式(1)來實現存在缺點,從式(1)中可以看出,其為一個遞推式,最先計算出最高有效位bn-1,最后計算出b0,一次轉化完成需要經過n-1個“異或門”的延時,當位數據位增加時,這將成為系統的運行瓶頸。在高速系統中表現的特別突出。提出一種改進的轉化單元。將式(1)轉化為式(2),如下所示:

可以看出,一次轉化只需要一個“異或門”的延時即可完成,但這種結構不適合FPGA中實現。在基本的門電路中,當門電路的扇入數據達到或者超過5時,延時將變得很大,而且大的扇入門電路的實現變得不現實且相當耗資源。將“異或門”的扇入數據限制在4以內(包括4個)。從“異或門”的規律中可以得出,任何變量與邏輯“0”異或,是其本身,而與“1”異或,是其相反變量。將待轉化的數據分為四位一組,第一組為(b3…b0),較高的位(如b7…b4)依此細分下去……最高的4位采用如式(2)中進行轉化,較低的4位如(bn-4…bn-7)采用如圖5的方式轉化……這種方式的轉化器相對于式(1)實現來說,在不增加門電路資源消耗的基礎上,能明顯提高轉化速度。|

2.2.3 相等判決單元

相等判決單元是一個二進制數比較器,當且僅當讀/寫地址指針完全相等時,給出空信號有效,否則空信號無效。

2.2.4 Rd_full信號產生單元

Rd_full信號產生單元的結構與FIFO滿(full)產生單元的結構相同,Rd_full信號是full信號在讀時鐘域中的一個復制信號,用于寫時鐘控制。在時鐘控制單元將詳細介紹其功能。

2.3 寫控制模塊

寫控制模塊的實現與讀模塊相似,由與讀模塊相應的單元組成。只是FIFO滿(full)時的產生邏輯為當讀地址指針與寫地址指針最高有效位不同,而其他位均完全相同時,滿信號有效。另一不同點體現在Wr_empty信號的產生上,Wr_empty只是FIFO為空(empty)信號時在寫時鐘域中的一個復制信號,用于讀時鐘的控制。

2.4 讀時鐘控制模塊

從以上的介紹中可以看出,各個模塊的工作統一由時鐘來管理,在高速的數字系統中,高速也將帶來高的能耗。筆者從實際工作中觀察發現,FIFO的工作是需要調配的,只有在DSP需要數據時,才需要FIFO處于工作狀態,而在DSP兩次需求之間,大量的時間中FIFO是處于空閑狀態(這樣的情形也符合大多數的實際應用)。可以充分利用這段空閑,讓FIFO既能在正常工作時高速而穩定地工作,同時在空閑時能盡可能降低能耗。時鐘控制模塊即能達到此目的。在空閑時,將FIFO的讀/寫時鐘停止,使空閑的模塊處于“休眠”狀態。但在正常工作時,時鐘能照常管理各個模塊。采用Virtex-4芯片內部自帶的時鐘管理模塊(Digital Clock Manager-DCM)[4]來實現。Virtex-4芯片中的DCM提供強大的時鐘管理功能,包括:時鐘去抖動、頻率合成、移相及動態時鐘配置。

應用中,主要利用其時鐘去抖動和動態時鐘配置兩項功能。在讀時鐘控制模塊中,當檢測到FIFO為空且Wr_empty同時有效時(如同時為高電平),通過DCM即可暫停讀時鐘。此時FIFO模塊中的所有讀組件將會停止運行。此時若寫入數據,由于Wr_empty處在寫時鐘域中,寫時鐘的控制下,Wr_empty將不會有效(變為低電平),此時通過DCM喚醒讀時鐘,可以正常讀出數據,同理可以控制寫時鐘的暫停與恢復。按照以上的原理設計,用Xilinx ISE 10.1仿真后,得到的仿真波形如圖6。clk_in為輸入時鐘,clk_out為經過控制的時鐘,而clk0_out是不經過控制的輸出時鐘。從圖中可以看出,當使能信號為有效(低電平)時,clk_out沒有時鐘輸出,而當使能信號無效時,clk_out時鐘正常恢復。可以通過將Wr_empty與empty經過“與非”后接到讀時鐘clk_en端即可。

2.5 寫時鐘控制模塊

寫時鐘控制模塊與讀時鐘控制模塊原理完全相同,只是輸入控制控制信號為Rd_full與full信號。

2.6 雙口RAM

雙口RAM的實現采用Xilinx的Virtex-4系列FPGA內部現有的資源,通過利用Virtex-4系列芯片中豐富的Block RAM資源,利用原語例化即可生成適合于實際應用需求的雙口RAM,參見文獻[4]。

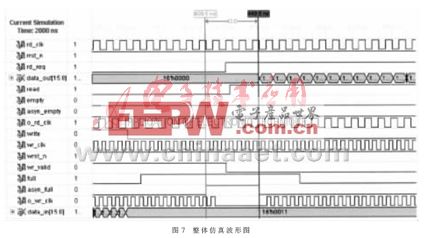

3 整體仿真結果

本方案的實現在Xilinx的ISE10.1上綜合,仿真后得到如圖7所示整體仿真波形。仿真中,為了便于查看結果,將實際受到控制的讀/寫模塊的時鐘引出,分別標記為o_wr_clk,o_rd_clk。由于截圖的限制,只能在圖中顯示FIFO滿的情況。空的情況類似。

fpga相關文章:fpga是什么

評論