基于FPGA的Viterbi譯碼器設計及實現

從以上的分析中我們可以得出一個很重要的結論:從T(i)時刻的狀態Sj(2(n-1)≥j≥0)生成的兩條支路,唯一不同的信息就是該時刻狀態Sj的輸入數據,Sj的上支路輸入的是0,下支路輸入的是1。因此,一個狀態可以只生成一條支路(上支路),另一條支路(下支路)的信息已經包括在這條支路中,要恢復出下支路只需要將上支路的輸入數據取反即可。圖4.2所示的ACS單元結構中的累加器可以減少一半的工作量,對于本文中的(2,1,7)卷積碼的譯碼器,即由每產生一位譯碼工作16個時鐘周期減少為8個時鐘周期(可將時鐘頻率降為原來的1/2),減少了復用次數,降低了ACS單元的復雜度和功耗。同時,由于ACS單元結構的優化,每個狀態只需要生成一條路徑,存儲的幸存路徑數也由原來的128條減少為64條,也同樣使結構變得簡單,功耗有所降低。

本文引用地址:http://www.104case.com/article/265114.htm由式(2)和式(3)可知,輸入數據(datain)不同,卷積碼的輸出C0和C1也不同,因此,同一狀態上支路的輸出與下支路不同,上下支路狀態輸出及譯碼器的輸入數據之間的關系如表1所示:

利用上下支路分支度量值的關系就可以從上支路路徑度量累加值中計算出下支路路徑度量累加值,用Verilog HDL語言描述為:

case(up_branch_metric)

2'b00: down_path_add_metric <= up_path_add_metric + 2'b10;

2'b01: down_path_add_metric <= up_path_add_metric;

2'b10: down_path_add_metric <= up_path_add_metric-2'b10;

default: down_path_add_metric <= 7'bxxx_xxxx;

endcase

另外,ACS單元中的累加器可以用超前進位加法器實現,這將使累加器不會成為速度的瓶頸。由于累加器使用固定長度的寄存器(本文中采用7bit的寄存器),因此在不斷累加過程中可能會發生溢出,影響譯碼結果。解決溢出常用的方法是到達譯碼深度時從所有狀態的路徑度量值中減去最小度量值。

3 幸存路徑管理單元

幸存路徑管理單元用來完成對幸存路徑的記錄,處理ACSU輸出的信息,為輸出判決作準備。SMU的實現主要有Register Exchange (寄存器交換)和Trace Back(回溯)兩種算法。由于寄存器交換算法比回溯有更小的譯碼延時,RE法中幸存路徑寄存器記錄了幸存路徑所對應的解碼信息,也就是譯碼輸出。采用這種方法消除了根據當前狀態往前追蹤的必要,因此寄存器交換提供了一種速度很高的譯碼操作。

4 判決輸出單元

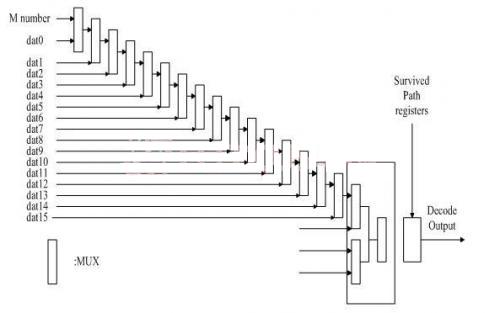

判決輸出單元(DOU)由兩部分組成:最小值選擇單元(MNSU:Minimum Number Select Unit)和譯碼輸出單元(DOU:Decode Output Unit)。最小值選擇單元是用來選出本文中前面4個ACS單元輸的路徑度量值中具有最小度量值的節點, 讀取該結點保存的幸存路徑,供譯碼輸出單元輸出譯碼值。判決輸出單元的結構如圖4所示:

圖4 判決輸出單元結構圖

5 控制單元

控制單元(CU)產生控制各模塊的時鐘信號,是所有模塊的有序運行的基礎。各時鐘信號功能如下:clk_load用于讀取前一時刻各狀態寄存器的內容,并產生各狀態上支路的狀態輸出值;clk_BM用于計算各狀態上支路的分支度量值并讀取前一時刻各狀態的路徑度量值;clk_Add用于計算各狀態上支路的路徑度量值;clk_restore用于暫存各狀態上支路度量值并恢復相應狀態下支路的路徑度量值;clk_C_S用于比較并選擇達到同一狀態的兩支路的路徑度量值的較小者,并存儲各狀態選擇的幸存路徑;clk_MNS用于選擇各狀態存儲的路徑度量值中的最小值,并保存該最小值對應的狀態;min_sel_1和min_sel_2分兩步選擇4個MNSU選擇結果的最小值,并選出最終的最小值對應的狀態;Decode_Output用于讀取該最小值對應狀態存儲的幸存路徑,并輸出譯碼結果。

二、項目實施方案

Viterbi譯碼器大致可以分為四個部分:支路度量模塊(BMU)、加比選模塊(ACS)、幸存路徑管理模塊(SMU)和輸出產生模塊。其 中支路度量模塊用于完成譯碼器輸入信號與網格圖上的可能路徑信號的分支度量計算;加比選模塊主要把前一個狀態的路徑度量與當前輸入信號的分支度量相加,以得到該分支的路徑度量,然后比較不同分支路徑度量的大小,同時找出最小的度量值,并更新該狀態的度量值,最后輸出狀態轉移信息;路徑管理模塊可對加比選單 元輸出的狀態轉移信息進行處理,以便為輸出判決做準備。輸出模塊可根據幸存路徑管理單元的輸出進行輸出判決,最后輸出譯碼信息。Viterbi譯碼器基本原理框圖如下所示。

fpga相關文章:fpga是什么

評論