基于FPGA的高速訪問USB設備設計

1.3.2 應用程序設計

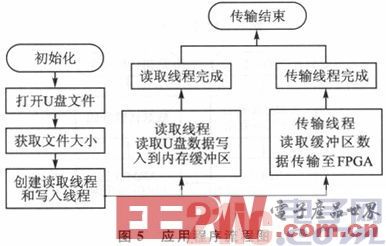

本文引用地址:http://www.104case.com/article/263272.htm本方案通過Linux系統的熱插拔機制自動啟動應用程序。在U盤插入USB接口后,Linux系統自動加載USB驅動和FPGA驅動并啟動應用程序。應用程序流程如圖5所示。

運行應用程序時,通過設置參數能使應用程序讀取U盤、移動硬盤甚至網絡上的文件,使方案具有很高的靈活性。應用程序使用了多線程技術來充分利用系統資源,使用兩個線程分別實現從U盤讀取數據存入緩沖區的過程和將緩沖區內的數據傳輸至FPGA的過程。在讀取線程或寫入線程中,可以加入數據處理代碼實現數據的預處理,減少FPGA工作量。應用程序分配了多個緩沖區提高性能,并使用了互斥鎖實現讀取線程與傳輸線程間的線程同步,確保數據正確傳輸。

1.4 ARM向FPGA傳輸數據設計

本方案在FPGA中實現一個異步RAM,其使用乒乓機制接收來自ARM處理器的數據,同時需要將異步RAM中的數據寫入DDR 2存儲器。異步RAM內部有兩個數據緩沖模塊。在乒乓機制中,兩個模塊分別執行不同的任務,當模塊1接收數據來自ARM處理器的數據時,模塊2將數據寫入DDR 2存儲器。當兩個模塊的任務都完成后,交換模塊1和模塊2的任務。與現有方案相比,本方案FPGA無需配置外部芯片,所需開發量較小。

2 測試與分析

2.1 傳輸速率測試

此測試傳輸3個不同大小的文件,記錄數據傳輸時間,從而獲得數據傳輸速率。

測試結果如表1所列。

由表1可知,在傳輸速率測試中,測得的最高數據傳輸速率為47.6 Mbps,比現有方案如CY7C67300、CH376的數據傳輸速率高。在傳輸速率測試中,傳輸100 KB文件的傳輸速率與傳輸1 MB和1 GB文件的傳輸速率相比偏低,而傳輸1 MB和1 GB文件的傳輸速率則相差不大。原因為:

①測試為先進行計時后開始傳輸,存在一段時間未傳輸數據。

②應用程序在傳輸開始前需要一段時間進行初始化,存在一段時間未傳輸數據。

在后兩種測試中,以上兩種未傳輸數據的時間占總時間的比重較低,因此數據傳輸速率較高。

2.2 傳輸準確率測試

此測試在FPGA內實現一個比較器,比較異步RAM接收到的數據與比較器內置數據是否一致,從而測試傳輸是否正確并確定正確率。經測試,此方案在傳輸過程中無差錯發生,傳輸正確率為100%。

結語

FPGA與ARM處理器相配合實現FPGA高速獲取U盤數據的方案,可以滿足FPGA高速讀取U盤數據的需求。在傳輸過程中無差錯,且具有良好的靈活性。本方案具有很高的實用價值。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

fpga相關文章:fpga是什么

linux相關文章:linux教程

評論