一種基于FPGA的UART接口開發方案

本文引用地址:http://www.104case.com/article/262819.htm

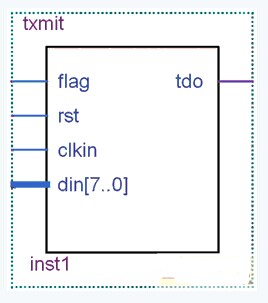

圖4 UART發送器符號圖

圖4 為UART發送器的符號圖,其中flag為輸入數據指示信號,rst為全局復位信號,clkin為輸入時鐘,din[70]為并行數據輸入端,tdo為串行數據輸出端。接收器在每個時鐘的上升沿檢測輸入數據指示信號,若檢測到其為高電平,則將并行輸入數據鎖存入內部的8比特移位寄存器,接下來先送出一個低電平并保持16個時鐘,然后每隔16個時鐘將移位寄存器中的數據移出一位,最后送出高電平,返回初始狀態。

系統調試

UART接收器和發送器可根據實際需要單獨使用,但在調試時為了方便,將兩者對接起來,如圖5所示。UART接收器的輸出與UART發送器的輸入相連,復位信號和時鐘信號共用,時鐘信號由片外晶振提供,輸入FPGA后通過鎖相環轉換為需要的頻率。

圖5 調試系統模塊圖

串口的調試需要借助于串口調試工具,可以用VC編程實現,也可以直接使用網上已有的調試工具。直接選用網上的串口調試助手進行了測試,將數據從計算機送出,經過UART接口接收后再送回計算機。經過長達數十分鐘的不間斷接收和發送后,將送回計算機的數據與原始數據進行比較,多次測試均沒有發生任何錯誤,這充分說明了這一UART接口程序具有高度的可靠性和穩定性,可以滿足設計要求。

結束語

基于FPGA設計和實現UART,可以用片上很少的邏輯單元實現UART的基本功能。與傳統設計相比,能有效減少系統的PCB面積,降低系統的功耗,提高設計的穩定性和可靠性,并可方便地進行系統升級和移植。

本設計具有較大的靈活性,通過調整波特率發生器的分頻參數,就可以使其工作在不同的頻率。采用16倍波特率的采樣時鐘,可以實時有效探測數據的起始位,并可對數據位進行“對準”中央采樣,保證了所采樣數據的正確性。該模塊可以作為一個完整的IP核移植進各種FPGA中,在實際應用時可嵌入到其他系統中,很容易實現和遠端上位機的異步通信。

電氣符號相關文章:電氣符號大全

fpga相關文章:fpga是什么

鎖相環相關文章:鎖相環原理

評論