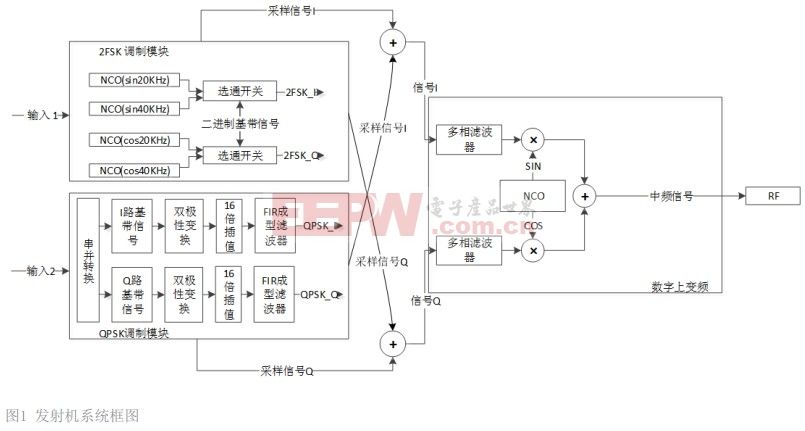

一種基于CPLD實現QPSK調制電路設計

3.1 電源模塊

本文引用地址:http://www.104case.com/article/262767.htm為電路提供5V電壓的設計實現方案有多種,如采用USB提供5V電壓也可以設計直流穩壓電源。直流穩壓電源的設計要先采用電源變壓器經過整流電路然后濾波最后穩壓這四部,設計實現起來相對復雜。設計中購買9V輸出電源,將9V電源轉化為5V電源。電路由一個7805芯片和2個電容組成,7805的1腳接電源電壓輸入,2腳接地,3腳經穩壓后輸出5V電壓。C1、C2用來濾出紋波。

3.2 時鐘信號模塊

時鐘電路模塊由2個反相器構成反饋,配合1個電容和2個電阻使晶振起振,來產生一個4MHz的時鐘。

3.3 基帶信號產生模塊

此模塊的作用是產生五種基帶信號(全0碼、全1碼、01碼、7位M序列和15位M序列)。

3.4 D/A模塊

調制模塊調制出來的信號是數字基帶信號,需要經過D/A轉換為模擬信號,在設計中選用DAC0832實現D/A轉換。

DAC0832輸出的是電流,但要求輸出是電壓,所以電路還必須經過一個運算放大器轉換成電壓。

3.5 濾波模塊

濾波電路在設計中采用的是一個壓控電壓源低通濾波器。其截至頻率為50KHz,增益為2,K=5.

4. 調制信號仿真

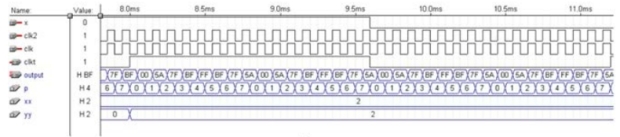

調制信號的仿真結果如下:

當輸入0/1碼時,由于寄存器y為2,所以循環輸出電平為005A7FBF.FFBF7F5A仿真波形如圖3所示。

圖3

當輸入15位M序列碼時,由于寄存器y值是變化的,所以輸出電平不是循環的,仿真波形如圖4所示。

圖4

5. 結束語

本次設計主要硬件模塊有基帶信號產生模塊、調制模塊、D/A轉換模塊和濾波模塊,其中為簡化設計系統設計供電模塊采用了5V電池供電,基帶信號產生模塊和調制模塊是設計中的關鍵點和難點,其基于CPLD設計,CPLD是一種整合性較高的邏輯邏輯元件。有高整合性的特點,故其有性能提升,可靠度增加,PCB面積減少和成本低等優點。

評論