基于FPGA的16抽頭FIR數字低通濾波器設計與仿真

摘要 采用改進并行分布式算法設計了一種16抽頭FIR數字低通濾波器,首先用Matlab工具箱中的FDATool設計濾波器系數,然后使用硬件描述語言Verilog HDL和原理圖,實現了子模塊和系統模塊設計,在Matlab與QuartusII中對系統模塊進行聯合仿真。仿真結果表明,設計系統性能穩定,濾波效果良好,且實用性較強。

本文引用地址:http://www.104case.com/article/262694.htm數字濾波器分為有限沖激響應(FIR)和無限沖激響應(IIR)兩種。其中,FIR數字濾波器在實現任意幅頻特性的同時能夠保證嚴格的線性相位特性。由于其單位沖激響應是有限的,沒有輸出到輸入的反饋,因此系統是穩定系統。FIR數字濾波器在通信、圖像處理、模式識別等領域有著廣泛應用。

在實時性要求較高的應用場合,相比于DSP芯片或專用芯片,采用可編程芯片FPGA實現FIR數字濾波器具有高速、高精度、高靈活性的優點。數字濾波器的設計方法有多種,常用的有窗函數法、頻率抽樣法和最佳一致逼近法,但這些設計方法在設計濾波器尤其是高階濾波器時工作量較大。而利用Matlab信號處理工具箱進行數字濾波器的設計,能夠減少工作量,提高設計效率。文中首先使用Matlab設計濾波器系數,然后利用FPGA實現系統。

在FPGA中,進行傳統乘法運算占用大量的硬件資源,分布式算法利用ROM查找表將固定系數的乘累加運算轉換成查表操作,避免了乘法運算,查表后的數據執行的都是簡單的加法運算,可以較大程度地提高運算速度。分布式算法分為全串行分布式算法和全并行分布式算法,全串行分布式算法資源消耗少但運算速度慢,全并行分布式算法資源消耗少但運算速度快。兼顧運算速度與資源消耗,本文采用改進并行分布式算法進行FIR數字濾波器設計。

1 FIR數字濾波器基本理論

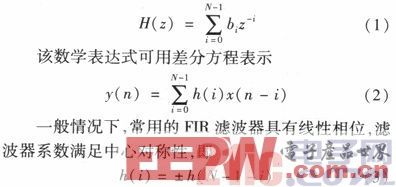

對于FIR數字濾波器系統,其沖激響應是有限長的,系統函數可記為

式中,x(n)是采樣輸入序列;h(i)是濾波器系數;N是濾波器抽頭數;y(n)是濾波器輸出序列。

2 分布式算法

分布式算法(Distributed Arithmetic,DA)是一項重要的FPGA技術,廣泛地應用在卷積、相關、DFF計算和RNS反演映射等乘積和中。有關DA算法的討論可以追溯到1973年Croisier發表的論文,而DA算法的推廣工作則由Peled和Liu完成。雖然DA算法較早被提出,但是一直到可編程門陣列的查找表結構出現,這種算法才重新受到重視,成為一種重要的FIR數字濾波器設計方法。

DA算法是一種以實現乘加運算為目的的運算方法,其與傳統實現乘加運算算法的不同之處在于執行部分積運算的先后順序不同。DA算法在完成乘加功能時是通過將各輸入數據每一位產生的部分積預先進行相加形成相應部分積,然后再對相應部分積進行加權累加形成最終結果;而傳統算法是等到所有乘積產生之后再進行相加來完成乘加運算。與傳統算法相比,DA算法可以大幅減少硬件電路規模,易實現流水線處理,提高了電路的執行速度。DA算法原理如下。

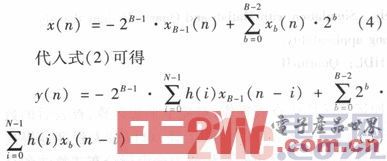

對于有符號系統,采用補碼實現,輸入序列x(n)表示為

式中,y(n)是輸出序列;x(n)是輸入序列;h(i)是濾波器系數;B是x(n)二進制補碼的位數;xb(n)是x(n)的第6位,N是濾波器抽頭數。

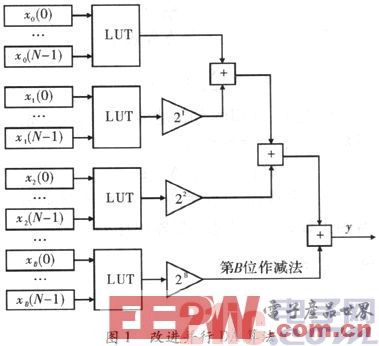

本文采用改進并行DA算法進行FIR數字濾波器設計,通過引入倍頻模塊減少LUT的個數來節省資源消耗,同時保證運算速度。該算法僅使用一個LUT并結合流水線寄存器的使用來提高系統運算速度。算法原理是讓輸入數據每一個相同位同時尋址,將尋址內容進行相應的移位累加操作得到最終輸出,算法如圖1所示。

3 濾波器系數設計與量化

文中濾波器系數通過Matlab工具箱中的FDATool進行設計,濾波器設計指標如下。濾波器類型:低通;設計方法:FIR Kaiser窗,Beta= 0.5;階數:15階;采樣頻率:10 MHz;截止頻率:1.5 MHz;輸入數據寬度:12位;濾波器系數寬度:12位。

由于FPGA只能進行定點數運算,需要將浮點濾波器系數量化為定點數。將h(n)擴大210倍,然后表示為12位二進制補碼。濾波器系數與量化補碼如表1所示。

4 FPGA實現

用FPGA設計FIR數字濾波器時,利用濾波器系數的對稱性,將16抽頭設計轉化為8抽頭設計。首先將輸入數據存入移位寄存器中,通過延時進行預相加,然后以預相加結果數據的相同位的值為地址進行查表操作。根據分布式算法公式,依次進行移位累加操作,但對數據最高位進行移位相減操作才能得到正確的濾波輸出。整個系統由時鐘控制模塊,數據輸入模塊,查找表模塊,移位累加模塊以及截位模塊組成。

4.1 時鐘控制模塊

采用的FPGA芯片是Altera公司的CycloneII系列EP2C5T144C6,其時鐘晶振是50 MHz。為提高系統運算速度,由于輸入數據是12位,數據輸入模塊一次輸出8位地址,因此需要設計一個采樣信號12倍頻模塊,即得到120 MHz信號。時鐘控制模塊主要包括采樣信號12倍頻模塊和采樣信號模塊。其中,采樣信號倍頻模塊利用QuartusII中PLL實現,采樣信號模塊利用倍頻模塊通過硬件描述語言Verilog HDL編程分頻實現。

4.2 數據輸入模塊

該模塊的功能是將輸入數據轉化為8位查找表的地址,包括移位寄存、預相加和并串轉換。首先將數據存入移位寄存器中,通過延時進行預相加,最后對預相加結果進行并串轉換。

4.3 查找表模塊

查找表模塊可以利用QuartusII中的lpm_rom實現,但需要手工計算每個地址對應的數據輸出,由于輸入8位地址數據,使用lpm_rom實現查找表的計算量過大,所以該模塊通過硬件描述語言Verilog HDL編程實現。模塊還可繼續拆分為4輸入或2輸入查找表。

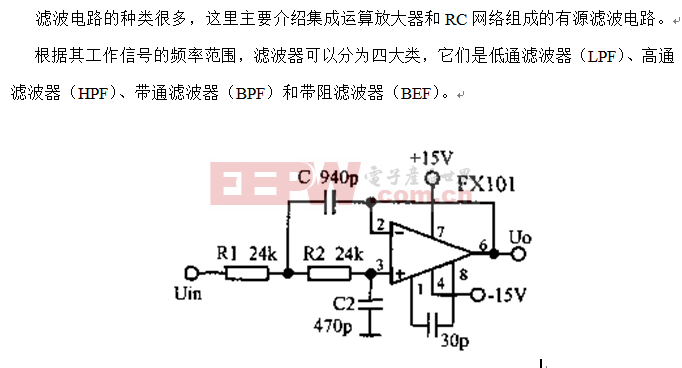

濾波器相關文章:濾波器原理

fpga相關文章:fpga是什么

濾波器相關文章:濾波器原理

低通濾波器相關文章:低通濾波器原理

電源濾波器相關文章:電源濾波器原理

晶振相關文章:晶振原理 數字濾波器相關文章:數字濾波器原理

評論