FPGA研發(fā)之道—總線

由于支持多個(gè)主設(shè)備和多個(gè)從設(shè)備進(jìn)行交互,那么對(duì)于多個(gè)主設(shè)備之間就存在競(jìng)爭(zhēng)。(從設(shè)備之間存在競(jìng)爭(zhēng)否?從設(shè)備之間是通過(guò)地址區(qū)分的,被動(dòng)接受主設(shè)備的訪問(wèn),不會(huì)存儲(chǔ)競(jìng)爭(zhēng)的問(wèn)題。)因此如何解決競(jìng)爭(zhēng),那就需要仲裁,即主設(shè)備誰(shuí)需要訪問(wèn)總線,則發(fā)起HBUSREQ,而仲裁器收到HBUSREQ,返回給相應(yīng)主設(shè)備HGRANT。此時(shí)該設(shè)備才能訪問(wèn)總線。除此之外AHB還有其他一些信號(hào),用于輔助整個(gè)系統(tǒng)的傳輸,感興趣的同志,可以看一下AMBA的總線規(guī)范。值得一提的是,作為一個(gè)總線規(guī)范,其提供了全集的解決方案,而作為實(shí)現(xiàn)部分,只需要在滿足規(guī)范的前提下,實(shí)現(xiàn)必要的功能即可,例如AHB總線中規(guī)定,其突發(fā)最大可1K字節(jié),但是作為一個(gè)從設(shè)備,不一定需要支持這么大的操作,即實(shí)現(xiàn)功能可在總線框架內(nèi)進(jìn)行裁剪,選擇實(shí)現(xiàn)支持的類型即可。

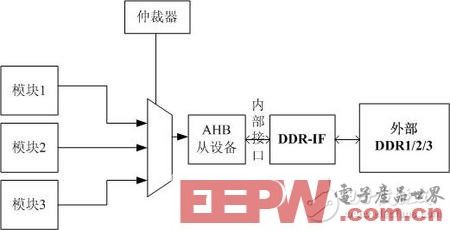

本文引用地址:http://www.104case.com/article/261790.htm在FPGA內(nèi)部設(shè)計(jì)中,經(jīng)常有多個(gè)主設(shè)備訪問(wèn)同一從設(shè)備的例子,例如內(nèi)部多個(gè)模塊都需要訪問(wèn)外部存儲(chǔ)器,其實(shí)現(xiàn)方式有多種,通過(guò)AHB的連接架構(gòu),可以實(shí)現(xiàn)一個(gè)標(biāo)準(zhǔn)、可擴(kuò)展的接口單元,用于訪問(wèn)外部存儲(chǔ)器。并且可以作為IP使用。AHB從設(shè)備只需要根據(jù)需要,支持某些burst傳輸即可。

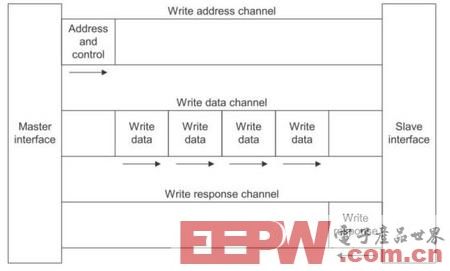

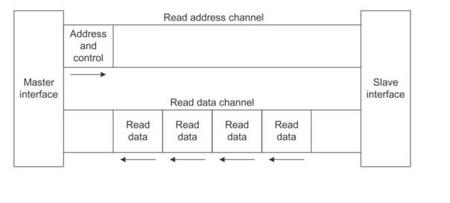

隨著SOC(片上系統(tǒng)的發(fā)展),對(duì)于高帶寬、低延時(shí)的總線需求更加迫切,ARM公司適時(shí)退出AXI(AMBA3.0)作為擴(kuò)展。

上圖分別是AXI接口的讀寫操作,分別可以看出,對(duì)于AXI總線來(lái)說(shuō),其有5組獨(dú)立的總線,分別是寫地址,寫數(shù)據(jù),寫響應(yīng),讀地址,讀數(shù)據(jù)信號(hào)。地址和數(shù)據(jù)信號(hào)分開(kāi),每組都有自己的控制信號(hào)。

每個(gè)通道中間沒(méi)有時(shí)序關(guān)聯(lián),如何進(jìn)行操作的?舉例來(lái)說(shuō)明,例如讀數(shù)據(jù)操作,實(shí)際上,主設(shè)備向從設(shè)備中寫了一個(gè)讀的命令,包括讀地址,burst大小,方式等。收到后從設(shè)備按照相應(yīng)的命令讀取相應(yīng)大小的數(shù)據(jù),傳回主設(shè)備,其操作可以簡(jiǎn)化的看做兩個(gè)緩沖區(qū)類型的操作,主設(shè)備將讀命令寫入從設(shè)備的命令緩沖區(qū),從設(shè)備取出后,根據(jù)命令將相應(yīng)的數(shù)據(jù)返回給主設(shè)備的接收緩沖區(qū)中。這種操作的好處顯而易見(jiàn),能夠最大限度的減少總線的開(kāi)銷,因此其讀與讀操作之間獨(dú)立,不用等待讀回,就可以發(fā)送下一次的讀信號(hào)。寫操作的流程亦然。

對(duì)FPGA設(shè)計(jì)來(lái)說(shuō),例如xilinx的接口IP(DDR例化時(shí)的接口),都已支持AXI的接口。FPGA工程師熟悉相應(yīng)的總線接口信號(hào)和特點(diǎn),對(duì)于技術(shù)方案選擇,IP使用和驗(yàn)證,都是非常重要的。盡量在設(shè)計(jì)中選擇標(biāo)準(zhǔn)總線接口,對(duì)于設(shè)計(jì)復(fù)用,模塊共享來(lái)說(shuō),則是必由之路。而模塊(IP)復(fù)用的益處隨著設(shè)計(jì)不斷增大將會(huì)不斷顯現(xiàn)。

fpga相關(guān)文章:fpga是什么

分頻器相關(guān)文章:分頻器原理

評(píng)論