關于常用通信接口技術的探討

對于第一種接口,位于同一塊電路板的網絡處理器芯片組和交換架構間的接口可用CSIXLevel1接口實現。該接口采用CSIXLevel1包格式,包括為交換架構提供路由指令的報頭,以及用于誤差檢測及糾正的報尾,還包括數據載荷本身。控制CSIX規范的網絡處理器論壇將進一步完善該規范,增加從一個NPU芯片組通過交換芯片傳至另一個NPU芯片的額外指令。這將成為CSIXLevel2規范的最主要推進力。該規范還定義了每個方向中使用至多128個HSTL一類I/O的電氣互連,其源同步時鐘頻率高達250MHz。CSIXLevel1協議與CSIXLevel1電氣規范無關,無論NPU芯片組和交換架構間的經由背板的通信采用何種電氣標準,仍可使用CSIXLevel1協議。

對于第二種接口,即NPU芯片組與交換架構間需要在通過背板通信,仍然可以使用CSIXLevel1協議,但這種電氣接口并不合適。信號將穿過連接器,從端口卡到達系統背板,經過數英寸到達另一個連接器,然后進入交換卡。有諸多原因使得越來越多的設計者選擇具有嵌入式時鐘的串行接口來實現這些連接。首先,串行接口可最大限度地減少電路板與背板連接器的引腳數,從而可減小插拔力及對操作系統中電路板的可能損害。其二,在信號中嵌入時鐘和數據的串行接口可完全避免時鐘偏移問題。時鐘偏移是PCB中數英寸長的并口所面臨的主要問題。其三,串行信號的背板設計者還可提高傳輸速率,因為不存在時鐘偏移,也就沒有對未來性能的限制。

被成功用作串行背板標準的接口是XAUI,它是為10千兆以太網開發的。該規范適用于通道排列電路,無論四通道軌線長度是否匹配,符合XAUI的器件均能接收無誤差數據。該接口使用差分電流模式邏輯信令,它還采用交流耦合模式,允許電路板間的參考電壓不同。

控制板接口

目前本文所提到的接口都用于數據通道,即數據從光纖傳輸介質到達交換架構,然后返回光纖通道。但由于通信系統具有復雜的控制板,負責統計數據收集、流量監視、系統管理及維護等功能,因此需要強大的處理能力運行軟件以實現這些功能。這些構建控制板處理器的接口正如設想的那樣,與數據通道的接口明顯不同。數據通道接口主要用于在兩個器件間傳輸數據(即點對點鏈接),控制板接口則是與具有不同元件的一個或多個微處理器相連接:背板收發器、DSP、數據板器件的控制端口等。實現這些靈活的互連需要完全不同類型的接口。

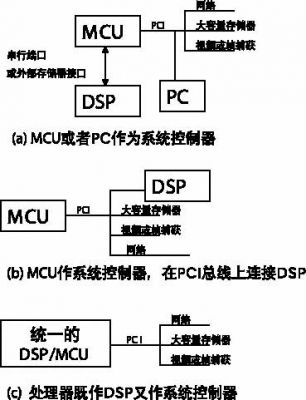

這類系統過去都是圍繞多點復接的中心總線構建的。實現PCI總線架構的32位/33MHz及最近采用的64位/66MHz標準已經用于通信系統中。最近64位/133MHzPCI-X更用于高端服務器。但是,由于數據板處理的帶寬已經增加,控制板的帶寬也要提高。很多設計者發現共享總線帶寬不足以滿足多個器件的需求。因此,出現一類新型接口。

這類新接口采用點至點連接,用源同步時鐘減少時鐘偏移。差分信令可提高數據傳輸率,減少交換噪聲和功耗。但真正的創新在于使用交換架構或通道器件,實現控制應用中所需的多點互連。

已獲得Motorola及RapidIO貿易聯合會支持的RapidIO是使用交換架構實現點至點鏈接的接口。

該接口的傳輸層規定數據如何封裝在包中,每個包都具有數據源和目標信息,交換架構將數據包送往合適的?用250MHz~1.0GHz雙數據速率。此外,串行RapidIO可使用具有8b/10b編碼的1通道或4通道數據,嵌入時鐘達3.125Gb/s,它還具有CML差分信令。

AMD及HyperTransport聯盟開發的HyperTransport使用通道器件實現點至點鏈接。數據以包的形式傳輸,每個包均包括數據源和目標信息。接收數據的通道器件按照數據包報頭確定是將數據傳至鏈中的下一個器件,還是直接處理數據。目前的HyperTransport規范需要寬度為2~16位的并行數據。未來規范可支持更高速率。PMC-Sierra和BroADCom已經為HyperTransport通信產品推出基于MIPS的處理器。

PCI-SIG已經推出高速率PCI-X。它們使用與最初PCI-X相同的64位總線帶寬,可支持雙數據速率和四倍數據速率。PCI-X533是速率最快的版本,最大總計帶寬達34.1Gb/s。

PCI-X的傳輸通訊協議、訊號和標準的接頭格式都與PCI一并兼容,可以使3.3V的32位PCI適配卡可以用在PCI-X擴充槽上。當然如果你愿意,也可以將64位PCI-X適配卡接在32位PCI擴充槽上,不過,頻寬速度將會大減

評論