SPI - 同步、全雙工的串行外設(shè)接口

SPI(Serial Peripheral Interface - 同步外設(shè)接口)總線是一種用于短距離通信(主要是嵌入式系統(tǒng)中)的同步串行通信接口規(guī)范,雖然沒有正式的國際標(biāo)準(zhǔn),但這種接口協(xié)議由Motorola發(fā)明迄今經(jīng)過很多廠商的支持,已經(jīng)成了一種事實(shí)標(biāo)準(zhǔn),被廣泛用于各種MCU處理器中,同傳感器,串行ADC、DAC、存儲器、SD卡以及LCD等進(jìn)行數(shù)據(jù)連接。由于沒有統(tǒng)一的國際標(biāo)準(zhǔn),SPI出現(xiàn)了很多不同的協(xié)議選項(xiàng),例如不同的Word大小;每個設(shè)備都有自己的協(xié)議定義,包括是否支持命令;有些設(shè)備只發(fā)送,其它的則只是接收;有的片選是高有效,有的則是低有效;有的協(xié)議先發(fā)送最低位。

本文引用地址:http://www.104case.com/article/202312/454088.htm

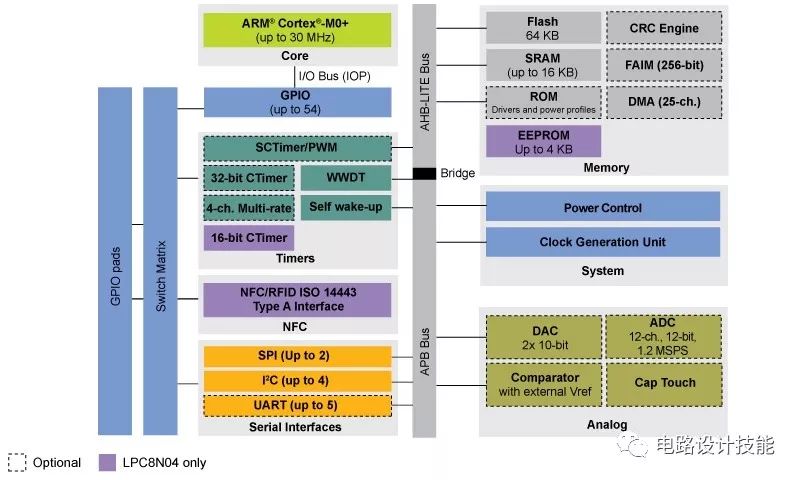

當(dāng)前的處理器中幾乎都有SPI和I2C和UART接口

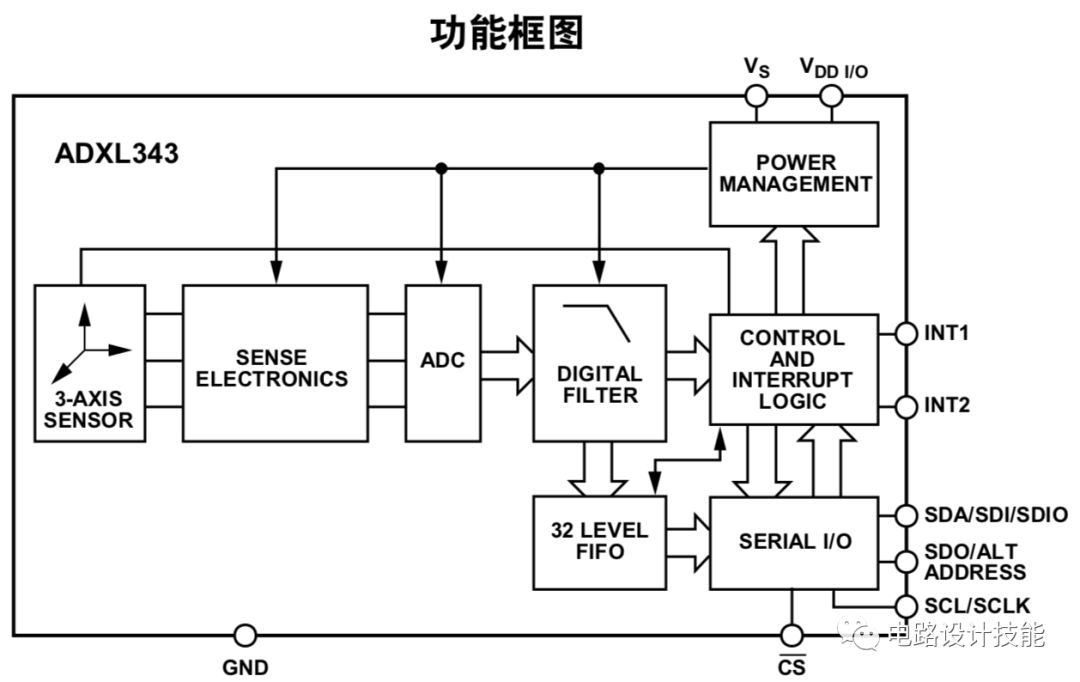

數(shù)字接口的傳感器也采用SPI和I2C

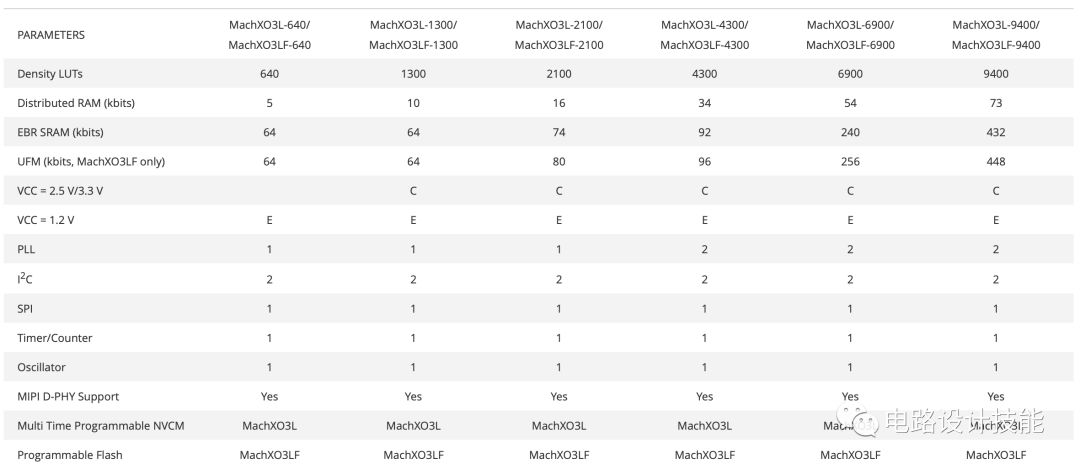

FPGA也將SPI、I2C硬化在器件內(nèi)部方便各種外設(shè)的連接

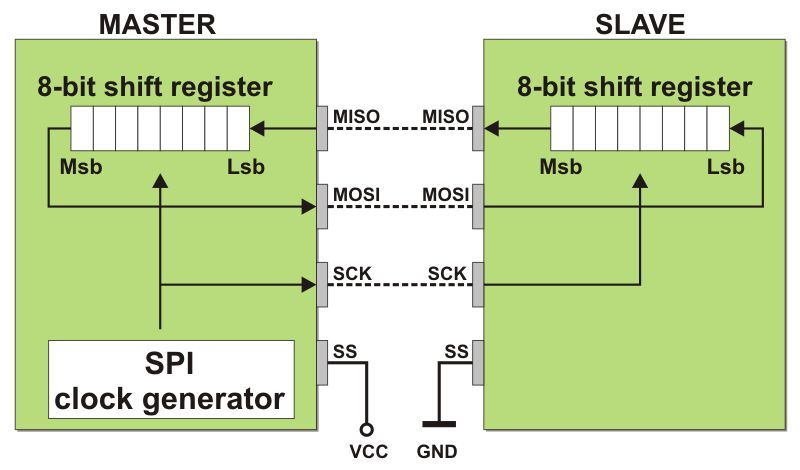

主、從器件之間的連接及數(shù)據(jù)傳輸方式

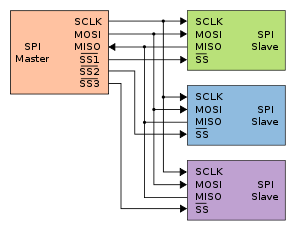

多個SPI設(shè)備可以通過全雙工的模式同單一的Master以主、從結(jié)構(gòu)進(jìn)行通信。主、設(shè)備發(fā)起讀、寫,多個從設(shè)備通過獨(dú)立的片選信號(SS - Slave Select)被尋址。

SPI總線:單主多從連接

有時SPI也被稱為四線串行總線,主要是與3線、2線、1線串行總線進(jìn)行區(qū)分,雖然SPI可以準(zhǔn)確地描述為一個同步串行接口,但它與同步串行接口(SSI)協(xié)議還是不同的,SSI同樣也是一種4線同步串行通信協(xié)議,但SSI采用的是差分信號,且只提供了一個簡單的通信信道。

動畫1顯示數(shù)據(jù)從器件A移出到器件B,從器件B移出到器件A.

SPI的技術(shù)實(shí)現(xiàn)

接口信號

工作模式

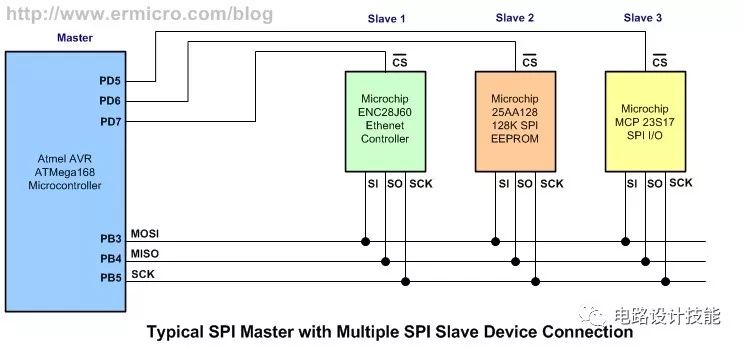

SPI總線可以工作在一個主設(shè)備/一個或多個從設(shè)備的模式。 如果只有一個從設(shè)備,SS管腳可以直接接地(從設(shè)備允許的話),有些從設(shè)備需要片選信號的下降沿來啟動傳輸,一個例子就是美信公司的串行ADC MAX1242,通過一個高電平到低電平的轉(zhuǎn)換標(biāo)記傳輸?shù)钠鹗肌H绻卸鄠€從設(shè)備,每個從設(shè)備需要一個獨(dú)立的SS信號連接到主設(shè)備。

多數(shù)從設(shè)備的輸出是三態(tài)的,當(dāng)該從設(shè)備沒有被選中的時候它們的MISO信號就為高阻(邏輯上斷開連接)。不具有三態(tài)輸出的器件是不能同其它器件共享SPI總線部分的,只能是一個從設(shè)備跟主設(shè)備相連。

SPI的時鐘采樣

通過多個從片選信號(SSN)配置

在標(biāo)準(zhǔn)的SPI配置中,主設(shè)備可以通過使能相應(yīng)的從設(shè)備,即通過將相應(yīng)設(shè)備的從選擇線(SSN或SS)設(shè)置為邏輯低電平,通過共享的公共數(shù)據(jù)線將數(shù)據(jù)寫入各個從設(shè)備或由各個從設(shè)備中讀取數(shù)據(jù)。 應(yīng)注意不要同時使能多個從設(shè)備,因?yàn)榉祷氐街髟O(shè)備的數(shù)據(jù)將在MISO線路之間的驅(qū)動器上產(chǎn)生競爭導(dǎo)致無法進(jìn)行數(shù)據(jù)的判讀。在某些應(yīng)用中不需要將數(shù)據(jù)返回給主設(shè)備,在這種情況下,如果主設(shè)備想要將相同的數(shù)據(jù)發(fā)送到多個從設(shè)備,則可以同時尋址多個從設(shè)備。

在多從設(shè)備選擇配置中,每個從設(shè)備都需要來自主設(shè)備的唯一從設(shè)備選擇線(SS、SSN或CSn)。如果主設(shè)備沒有足夠的I/O引腳用于所需數(shù)量的從設(shè)備,則使用解碼/解復(fù)用器(例如74HC(T)238(3到8線)來實(shí)現(xiàn)I/O擴(kuò)展)。

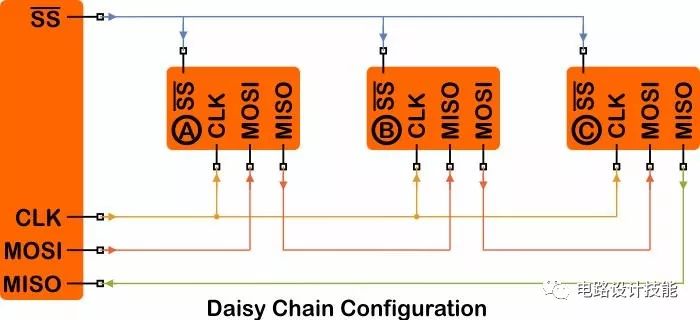

菊花鏈配置

在這種配置中,數(shù)據(jù)從一個設(shè)備移動到下一個設(shè)備, 最終的從設(shè)備可以將數(shù)據(jù)返回給主設(shè)備(給FPGA編程的JTAG在給多個器件編程的時候也常用這種方式)。

在菊花鏈配置中,所有從設(shè)備共享一條公共的從選擇線(SS)。 數(shù)據(jù)從主設(shè)備傳輸?shù)降谝粋€從設(shè)備,然后從第一個從設(shè)備傳輸?shù)降诙€從設(shè)備,依此下去,數(shù)據(jù)沿著線路級聯(lián),直到系列中的最后一個從設(shè)備,最后的一個從設(shè)備使用其MISO線路將數(shù)據(jù)傳送到主設(shè)備。

這種配置非常適合于主設(shè)備的信號引腳有限的場景。

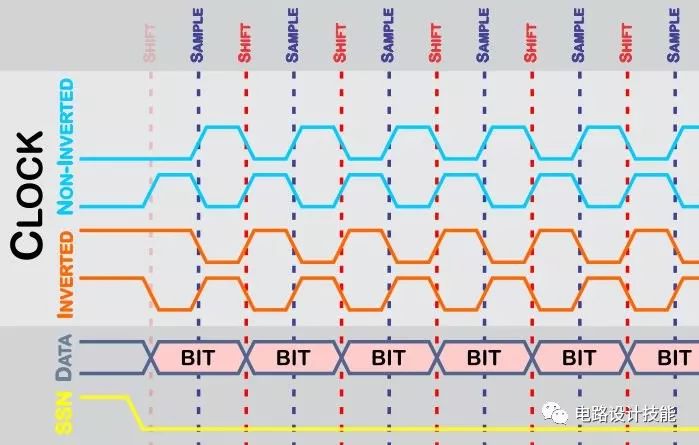

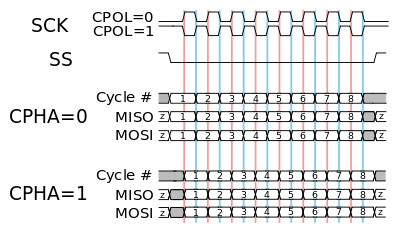

4種傳輸模式

每次數(shù)據(jù)傳輸都是先將SSN(有的器件命名為SS,從選擇線)被驅(qū)動為邏輯低電平時開始。由時鐘的極性(CPOL)和相位(CPHA)構(gòu)成了4種不同的數(shù)據(jù)傳輸模式(0,1,2,3),分別對應(yīng)四種可能的時鐘配置。

具有非反相時鐘極性(即,當(dāng)從器件選擇轉(zhuǎn)換為邏輯低時,時鐘處于邏輯低電平):

使用反相時鐘極性(即,當(dāng)從器件選擇轉(zhuǎn)換為邏輯低時,時鐘處于邏輯高電平):

由于主設(shè)備一般為可以編程各種模式的控制器/處理器或者可以靈活編程的FPGA,因此在使用SPI連接的時候要認(rèn)真閱讀自己選用的從設(shè)備的工作模式,以便在時序上滿足傳輸?shù)囊蟆?/p>

SPI數(shù)據(jù)傳輸?shù)闹髟O(shè)備端代碼示例

以下是一段主設(shè)備工作于CPOL=0、CPHA=0模式時的數(shù)據(jù)傳輸?shù)拇a,每次傳輸為8位,此示例采用C語言。由于工作于CPOL=0, 在片選被選中之前要把時鐘拉低,片選信號必須使能,也就是說在數(shù)據(jù)傳輸之前要將外設(shè)的片選信號電平變低,并在傳輸結(jié)束以后不再“使能”。 多數(shù)的外設(shè)允許或需要在片選信號選中以后進(jìn)行多次傳輸,次子程序也許需要被多次調(diào)用。

/*

* Simultaneously transmit and receive a byte on the SPI.

*

* Polarity and phase are assumed to be both 0, i.e.:

* - input data is captured on rising edge of SCLK.

* - output data is propagated on falling edge of SCLK.

*

* Returns the received byte.

*/uint8_t SPI_transfer_byte(uint8_t byte_out){

uint8_t byte_in = 0;

uint8_t bit; for (bit = 0x80; bit; bit >>= 1)

{

/* Shift-out a bit to the MOSI line */

write_MOSI((byte_out & bit) ? HIGH : LOW); /* Delay for at least the peer's setup time */

delay(SPI_SCLK_LOW_TIME); /* Pull the clock line high */

write_SCLK(HIGH); /* Shift-in a bit from the MISO line */

if (read_MISO() == HIGH)

byte_in |= bit; /* Delay for at least the peer's hold time */

delay(SPI_SCLK_HIGH_TIME); /* Pull the clock line low */

write_SCLK(LOW);

}

return byte_in;

}SPI的優(yōu)點(diǎn)和缺點(diǎn)

優(yōu)點(diǎn)

缺點(diǎn)

SPI的主要應(yīng)用

與并行I/O總線相比,SPI能夠大大節(jié)省電路板的空間,因此在嵌入式系統(tǒng)中發(fā)揮了重要作用,對于大多數(shù)片上系統(tǒng)處理器而言都是如此,這些處理器都具有較高端的32位處理器,例如使用ARM、MIPS或PowerPC的處理器以及其它微控制器,如AVR、PIC和MSP430等。 這些芯片通常包括能夠以主模式或從模式運(yùn)行的SPI控制器,也可以使用SPI接口對系統(tǒng)內(nèi)可編程AVR控制器(包括空白控制器)進(jìn)行編程。

基于芯片或FPGA的設(shè)計有時使用SPI在內(nèi)部的組件之間進(jìn)行通信,即便是片內(nèi),其面積的節(jié)省也像電路板上一樣非常重要。

全雙工功能使SPI非常簡單、高效、適用于單主/單從機(jī)應(yīng)用。 一些設(shè)備使用全雙工模式為數(shù)字音頻、數(shù)字信號處理或電信信道等應(yīng)用實(shí)現(xiàn)高效、快速的數(shù)據(jù)流,但大多數(shù)現(xiàn)成的芯片都采用半雙工請求/響應(yīng)協(xié)議。

SPI被用來同各種外設(shè)通信,例如:

對于高性能系統(tǒng),F(xiàn)PGA有時使用SPI作為主機(jī)的從機(jī)接口、作為傳感器的主機(jī)、或者如果它們是基于SRAM的,則用于引導(dǎo)的閃存。

雖然SPI總線和JTAG(IEEE 1149.1-2013)協(xié)議之間存在一些相似之處,但它們不可互換。 SPI總線用于器件外設(shè)的高速、板載初始化,而JTAG協(xié)議旨在通過板外控制器(有著比較低精度的信號延遲和偏斜參數(shù))提供對I/O引腳的可靠測試訪問。 JTAG協(xié)議不是嚴(yán)格意義上的電平敏感接口,它通過降低時鐘速率或改變時鐘的占空比來支持JTAG器件在建立和保持違規(guī)的情況下能夠恢復(fù)。 因此,JTAG接口不是用來支持極高的數(shù)據(jù)速率的。

協(xié)議分析及調(diào)試設(shè)備

主適配卡

有許多使用USB的硬件解決方案可以利用運(yùn)行Linux、Mac或Windows的計算機(jī)支持SPI主控和/或從屬功能。其中許多還提供腳本和/或編程功能(Visual Basic,C / C ++,VHDL等)。

SPI主機(jī)適配器允許用戶直接從PC在SPI總線上扮演主站的角色。它們用于嵌入式系統(tǒng)、芯片(FPGA/ASIC/SoC)和外設(shè)測試、編程和調(diào)試。

SPI適配器的關(guān)鍵參數(shù)包括:串行接口支持的最大頻率、命令到命令延遲以及SPI命令的最大長度。目前市場上可以找到支持高達(dá)100MHz串行接口的SPI適配器,幾乎無限制的訪問長度。

SPI協(xié)議是事實(shí)上的標(biāo)準(zhǔn),一些SPI主機(jī)適配器還能夠支持超越傳統(tǒng)4線SPI的其他協(xié)議(例如,支持四SPI協(xié)議或其他源自SPI的定制串行協(xié)議)。

SPI適配器的示例(制造商按字母順序):

| 生產(chǎn)商 | SPI Host適配卡 | Host總線 | 支持的總線協(xié)議 | 最高頻率 |

|---|---|---|---|---|

| Byte Paradigm | SPI Storm | USB | SPI, dual/quad, custom | 100 MHz |

| Corelis | BusPro-S | USB | SPI, dual/quad | 60 MHz |

| HydraBus | HydraBus-HydraFW | USB | SPI | 42 MHz |

| Microchip | MCP2210 Kit | USB | SPI | 12 MHz |

| National Instruments | USB-8452 | USB | I2C, SPI | 50 MHz |

| Total Phase | Cheetah SPI Host Adapter | USB | SPI | 40 MHz |

| Total Phase | Promira Serial Platform | USB, Ethernet | I2C, SPI, single/dual/quad, and eSPI | 80 MHz |

| Dangerous Prototypes | Bus Pirate | USB | 1-Wire, I2C, SPI, JTAG*, Asynchronous serial, Scriptable binary bitbang, UART | varies |

協(xié)議分析儀

SPI協(xié)議分析儀可以對SPI總線進(jìn)行采樣并對電信號進(jìn)行解碼分析,以提供在特定總線上傳輸?shù)臄?shù)據(jù)的更高級別視圖。SPI協(xié)議分析儀示例(制造商按字母順序排列):

| 廠商 | 分析儀的型號 | 上位機(jī)的總線 | 支持的總線協(xié)議 | 最高采樣率 | 其它 |

|---|---|---|---|---|---|

| Saleae Logic Pro 16 | USB | SPI, I2C, serial, custom | 500 Mega-samples/second | Analog (50Msps) | |

| TechTools | DigiView Logic Analyzers | USB | SPI, I2C, CAN, Async, Sync, I2S, State, Custom | 500Msps | Extendable with custom plugins |

| Total Phase | Beagle I2C/SPI Protocol Analyzer | USB | SPI, I2C, MDIO | 50Msps | |

| Total Phase | Promira Serial Platform | USB, Ethernet | eSPI |

示波器

每個主要的示波器供應(yīng)商都為SPI提供了基于示波器的觸發(fā)和協(xié)議解碼,大多數(shù)支持2線、3線和4線SPI。 觸發(fā)和解碼功能通常作為可選附件提供。SPI信號可通過模擬示波器通道或數(shù)字MSO通道進(jìn)行訪問。

邏輯分析儀

在開發(fā)和/或排除SPI總線故障時,檢查硬件信號非常重要。 邏輯分析儀是收集、分析、解碼和存儲信號的工具,因此人們可以用它來查看高速波形。 邏輯分析儀顯示每個信號電平變化的時間戳,這有助于發(fā)現(xiàn)協(xié)議問題。大多數(shù)邏輯分析儀都能夠?qū)⒖偩€信號解碼為高級協(xié)議數(shù)據(jù)并顯示ASCII數(shù)據(jù)。

評論