超寬帶(UWB)定位系統(tǒng)發(fā)射機基帶的系統(tǒng)設計,功能模塊分解、硬件實現(xiàn)

4.1.7導頻和保護子載波插入

在本文設計中,導頻和保護子載波插入也是利用雙口塊RAM來實現(xiàn)的,根據(jù)子載波映射到IFFT的輸入端口的編號,將相應數(shù)據(jù)對應的復數(shù)寫入雙口塊RAM的地址中,當進行IFFT變換時,只需將其順序讀出即可。

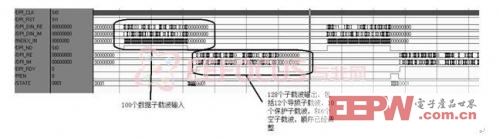

對工程文件進行綜合、布局布線后仿真,得到如圖4.22所示結(jié)果。

圖4.22 導頻和保護子載波插入仿真結(jié)果

其中PIEN=1代表導頻與保護子載波插入開始,將插入后的數(shù)據(jù)從雙口RAM中順序讀出,就得到了最后輸出的結(jié)果。

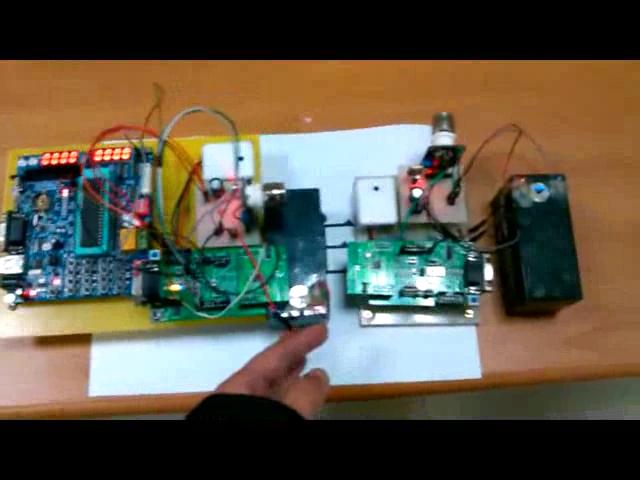

使用Chipscope添加觀察信號采樣時鐘、觸發(fā)信號和待觀察信號,重新綜合、布局布線生成bit文件,下載到目標板后用ChipScope進行在線測試,得到觀測結(jié)果如圖4.23所示。通過仿真結(jié)果和在線測試結(jié)果的對比,可以驗證設計的正確性。

圖4.23 導頻和保護子載波插入在線測試結(jié)果

4.1.8IFFT變換

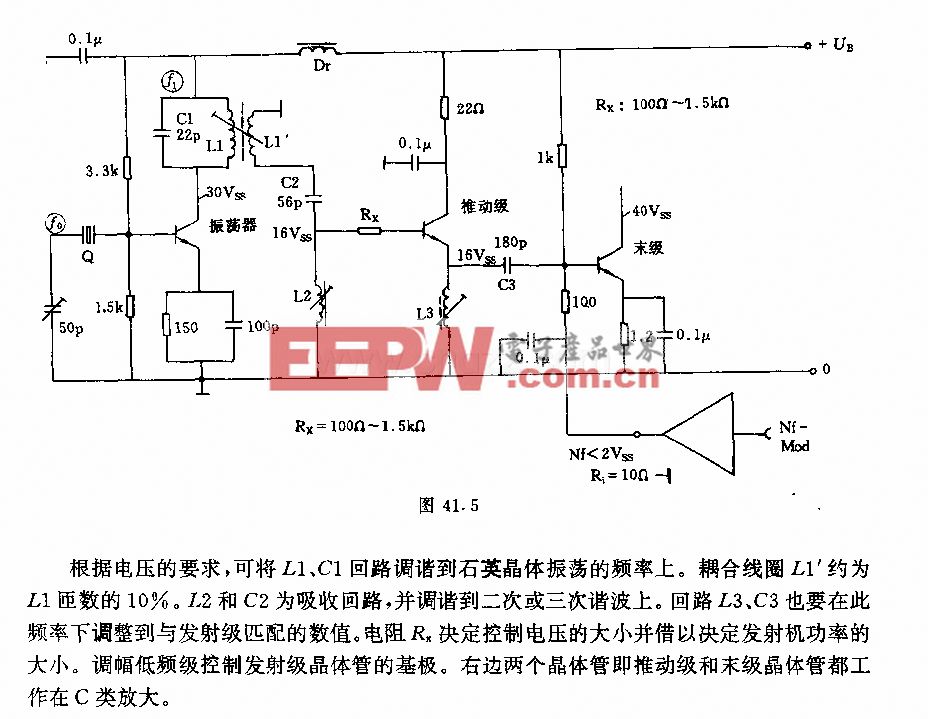

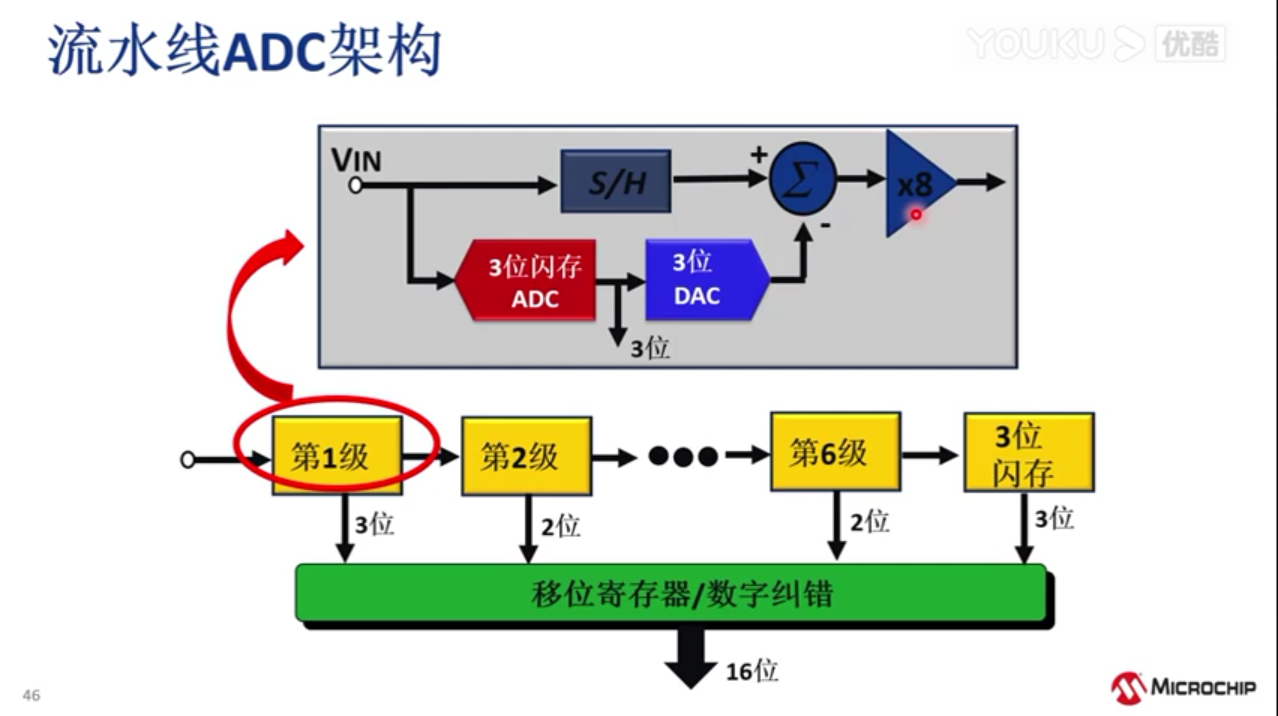

在MB-OFDM-UWB系統(tǒng)中,OFDM調(diào)制和解調(diào)可以分別通過IFFT/FFT來實現(xiàn),頻域數(shù)據(jù)符號經(jīng)過N點的IFFT運算變換為時域信號,接下來便可以傳輸給射頻前端發(fā)射出去。

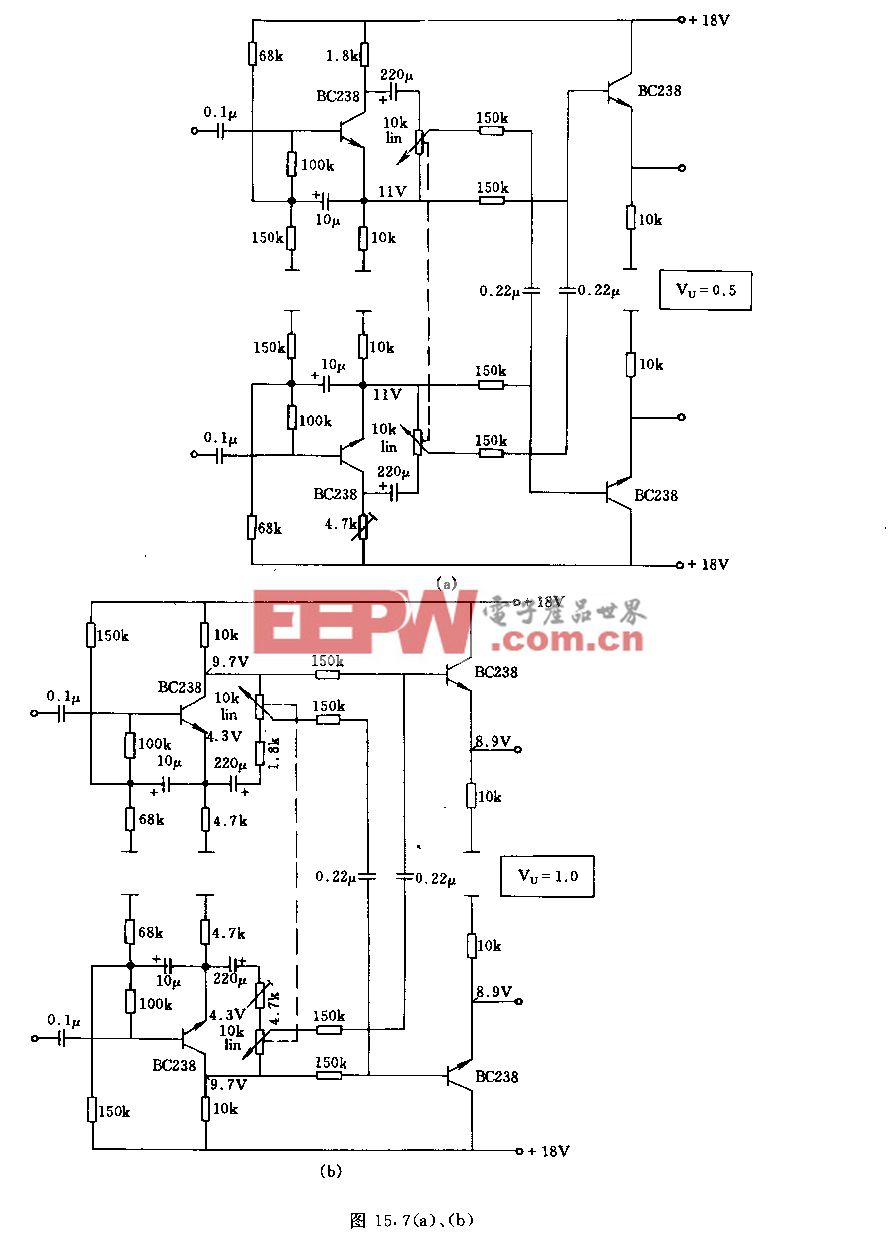

本文利用Xilinx的Ipcore FFT v5.0來實現(xiàn)IFFT功能,F(xiàn)FT v5.0核采用DIT的Cooley-Tukey算法,提供4種不同的結(jié)構: Pipelined, Streaming I/O, Radix—4 Burst I/O,Radix—2 Burst I/O,Radix—2 Lite Burst I/O,

在這四種結(jié)構中,第一種流水式輸入/輸出可以實現(xiàn)連續(xù)幀處理,速度最快,但也需要最多的乘法器。基4突發(fā)式輸入/輸出結(jié)構擁有較小的結(jié)構,需要較少的資源,但必須等待前一幀數(shù)據(jù)處理完成,才能處理下一幀數(shù)據(jù),轉(zhuǎn)換時間較第一種長。另外兩種基2結(jié)構較為簡單,使用資源也最少,但是速度也是最慢的。

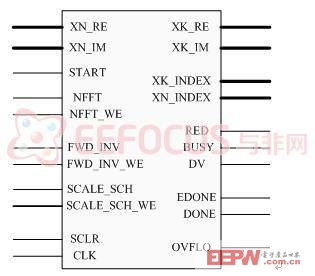

基于運算速度和芯片資源的綜合考慮,本文采用Radix—4 Burst I/O結(jié)構的IFFT配置方式,F(xiàn)FT IP核模塊框圖如圖所示[32]。

圖4.24 FFT IP核模塊框圖

上面已經(jīng)講到,采用Burst I/O模式的IFFT核需要等待前一幀數(shù)據(jù)處理完成才能輸入下一幀,如果輸入使用原來的SYS_CLK_D時鐘來作為IFFT變換的時鐘,在下一幀來的之前是無法完成計算的,因此,需要對輸入IFFT的數(shù)據(jù)進行時鐘轉(zhuǎn)換,將速度提升一倍,以滿足時序要求。當IFFT變換完成后,再利用時鐘轉(zhuǎn)換模塊將數(shù)據(jù)調(diào)整回原來的速率。實現(xiàn)框圖如圖4.25所示

圖4.25 IFFT 實現(xiàn)框圖

仿真結(jié)果如圖4.26所示

圖4.26 IFFT模塊仿真結(jié)果

從圖中可以看出,每組輸入數(shù)據(jù)都能滿足在上一組數(shù)據(jù)輸出結(jié)束后開始輸入,從而滿足突發(fā)式輸入輸出的設計要求。使用Chipscope添加觀察信號采樣時鐘、觸發(fā)信號和待觀察信號,重新綜合、布局布線生成bit文件,下載到目標板后用ChipScope進行在線測試,由于受到資源的限制,采樣深度和采樣信號個數(shù)都受到限制,只能夠采樣一些關鍵的數(shù)據(jù),得到觀測結(jié)果如圖4.27所示。通過仿真結(jié)果和在線測試結(jié)果的對比,可以驗證設計的正確性。

圖4.27 IFFT在線測試結(jié)果

4.2本章小結(jié)

在這一章中,根據(jù)第三章的設計方案,完成對各個模塊的Verilog HDL程序編寫仿真,以及在ISE仿真平臺上進行詳細的驗證,我們選用Xilinx公司的Spartan-6型FPGA作為目標硬件,使用Verilog HDL作為描述語言。對于硬件實現(xiàn)的驗證調(diào)試采用了Xilinx公司的在線片內(nèi)信號分析工具ChipScope Pro,通過FPGA上的實測結(jié)果與Modelsim 上的仿真的比較結(jié)果驗證設計的正確性。

pa相關文章:pa是什么

評論