無源高頻RFID芯片的FPGA原型驗證平臺設計

射頻識別即RFID技術(shù)又稱電子標簽、無線射頻識別,是一種通信技術(shù)[1].RFID技術(shù)作為物聯(lián)網(wǎng)發(fā)展的關(guān)鍵技術(shù),其應用必將隨著物聯(lián)網(wǎng)的發(fā)展而擴大。常用的RFID分低頻、高頻、超高頻3種,其中高頻RFID典型工作頻率為13.56 MHz,一般以無源為主。高頻標簽比超高頻標簽具有價格便宜、節(jié)省能量、穿透非金屬物體力強、工作頻率不受無線電頻率管制約束的優(yōu)勢,最適合應用于含水成分較高的物體中,例如水果等。

基于FPGA的原型驗證方法憑借其速度快、易修改、真實性的特點,已經(jīng)成為ASIC芯片設計中重要的驗證方法[2].本文主要描述高頻RFID芯片的FPGA原型驗證平臺的設計,并給出驗證結(jié)果。

1 RFID芯片的FPGA原型驗證環(huán)境概述

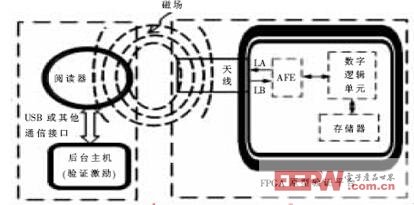

一套完整的RFID系統(tǒng)是由閱讀器(Reader)、電子標簽芯片(Tag)也就是所謂的應答器(Transponder)及應用軟件三部分組成[3].

電子標簽芯片的FPGA原型驗證環(huán)境也是一套完整的RFID系統(tǒng),用FPGA原型驗證平臺替代上述的電子標簽芯片(Tag),使用上層的應用軟件開發(fā)驗證激勵。通過閱讀器與FPGA原型驗證平臺進行通信來實現(xiàn)對FPGA中的數(shù)字邏輯進行驗證的目的。圖1是典型的RFID芯片的FPGA原型驗證環(huán)境原理圖。

圖1 RFID芯片和FPGA原型驗證環(huán)境原理圖

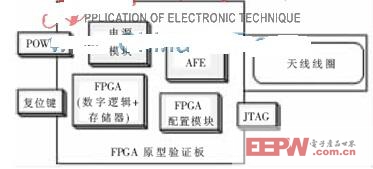

圖2 驗證平臺硬件系統(tǒng)結(jié)構(gòu)圖

2驗證平臺的硬件設計

2.1驗證平臺硬件系統(tǒng)結(jié)構(gòu)

FPGA原型驗證平臺利用自身的硬件資源,模擬實現(xiàn)RFID芯片的各功能模塊。其中數(shù)字邏輯單元和存儲器是FPGA原型驗證的對象,由FPGA內(nèi)部的資源實現(xiàn)。圖2為驗證平臺硬件系統(tǒng)結(jié)構(gòu)圖。

下面詳細介紹FPGA器件選型、模擬射頻前端(AFE)電路設計、天線設計及調(diào)試,其中重點是FPGA器件選型和模擬射頻前端電路設計,難點是天線設計及調(diào)試。

2.2 FPGA器件選型

FPGA原型驗證平臺中FPGA器件選型主要考慮FPGA的邏輯資源、存儲資源、I/O資源和時鐘資源,另外兼顧器件的供貨渠道、速度等級、溫度等級等。

FPGA的邏輯資源應為待驗證ASIC邏輯門數(shù)的2~3倍或更高;存儲資源、滿足待驗證ASIC存儲資源的需求,主要是Blockram資源,I/O資源,用戶可配置的I/O數(shù)量除了滿足ASIC設計的數(shù)字端口信號需求外,還要預留一定量的調(diào)試I/O;時鐘資源,主要指全局時鐘數(shù)量,ASIC低功耗設計會用到大量的門控時鐘,轉(zhuǎn)化門控時鐘需用到FPGA的全局時鐘資源。

根據(jù)以上原則,本次FPGA采用Xilinx Spartan3-1000芯片。該芯片可編程約10萬門的ASIC邏輯;16組blockram,提供432 kbit地址空間;8個全局時鐘bufer用于定義時鐘;4個DCM模塊,可以精確地實現(xiàn)內(nèi)部時鐘分頻、倍頻;用戶可用的I/O多達173個。

本次待驗證的RFID芯片的數(shù)字邏輯規(guī)模約為1萬門,存儲器容量為1 kbit,時鐘網(wǎng)絡簡單,端口I/O少。實驗證明,該FPGA的資源完全滿足RFID芯片的原型驗證需求。

2.3模擬射頻前端(AFE)電路設計

在搭建RFID芯片的驗證平臺時,模擬射頻前端(AFE)通常采用分立元件實現(xiàn)。分立器件實現(xiàn)的AFE電路穩(wěn)定性差,受環(huán)境影響比較大,調(diào)試難度大。例如,包絡檢波器的輸出幅值隨場強變化較大,導致電壓比較器工作失常,由此轉(zhuǎn)換出的數(shù)字信號出現(xiàn)錯誤。

為改善以上穩(wěn)定性差的問題,本次模擬射頻前端采用AFE IC實現(xiàn)。AFE IC完成信號能量交流直流轉(zhuǎn)換、限壓、穩(wěn)壓、信號調(diào)制和解調(diào)、時鐘產(chǎn)生及上電復位等功能。該芯片經(jīng)過了成熟的測試,穩(wěn)定性好,受磁場環(huán)境的影響小,電路穩(wěn)定性大大增強,調(diào)試風險大大降低。圖3為模擬射頻前端(AFE)與其他功能模塊的連接關(guān)系圖。

圖3 AFE與FPGA的連接關(guān)系圖

2.4天線設計及調(diào)試

2.4.1天線設計原理

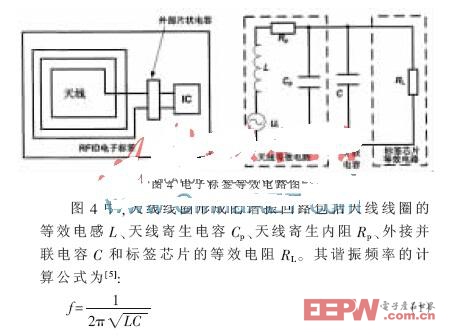

高頻電子標簽的天線線圈進入閱讀器產(chǎn)生的交變磁場時,讀寫器與標簽之間可等效為變壓器耦合方式。讀寫器天線相當于變壓器的初級線圈,標簽上的天線相當于次級線圈[4].對于無源電子標簽,電子標簽可以簡化為天線與芯片的直接電連(標簽天線可等效為天線等效內(nèi)阻與等效感應電壓源的串聯(lián)組合,標簽芯片可等效為純阻抗)。圖4為無源高頻電子標簽等效電路圖。

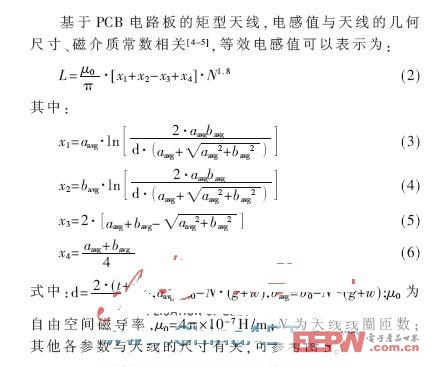

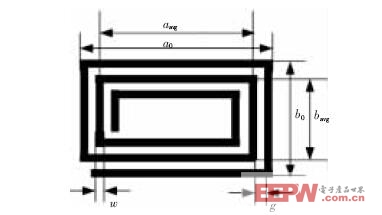

符合ISO/IEC l5693標準的RFID系統(tǒng),電子標簽和閱讀器之間的載波頻率為13.56 MHz.為了保證閱讀器與標簽之間的良好通信,標簽的諧振頻率要接近13.56 MHz.本文描述的FPGA原型驗證平臺設計中,天線設計也是基于以上理論模型,設計成矩型天線。

ISO/IEC 15693-1協(xié)議中規(guī)定,標簽天線尺寸最大不超過86 mm×54 mm,典型線圈有3~6匝[3].這樣可以根據(jù)實際的設計需求先確定天線尺寸,本次設計的天線長和寬分別為79 mm和47 mm,天線線圈的線寬為6 mil,線圈間距為9 mil,線圈匝數(shù)為4.

圖5 RFID標簽天線尺寸參數(shù)示意圖

評論