NI矢量信號收發器的FPGA編程

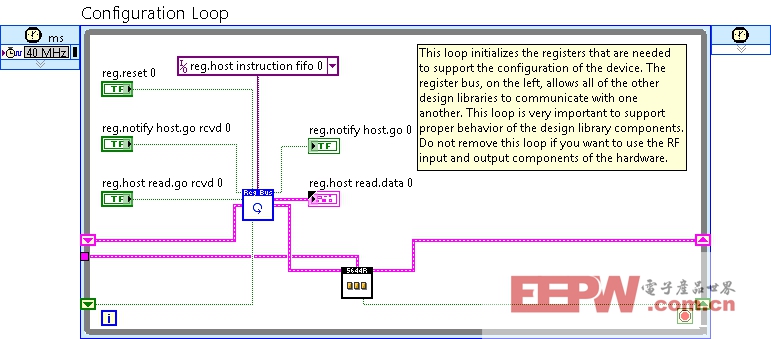

VST Streaming項目樣例的頂層FPGA VI的架構與簡單 VSA/VSG項目樣例相近。然而如果仔細考察,會發現要簡單得多。可以明顯看出,VST Streaming沒有代碼量極多的配置過程。配置循環也簡單得多,只有一條寄存器總線而非兩條,并且所有子系統均包在一個子VI中。

圖 13.VST Streaming項目樣例中的FPGA VI配置回路,只有一個寄存器總線接口,比Simple VSA / VSG要簡單得多

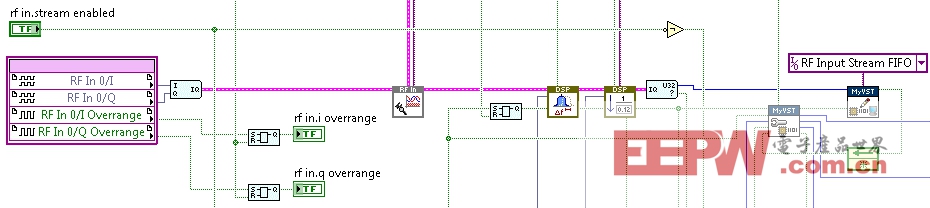

VST Streaming項目樣例沒有獨立的采集和發生循環,而是所有模擬I/O均采用一個循環。對于要求RF輸入輸出之間的相位關系已知的應用,由于ADC和 DAC使用相同的采樣時鐘,此架構提供了兩者之間的確定性同步。DSP和VST Streaming項目樣例的校準類似于VSA / VSG。

兩個項目樣例FPGA VI之間的主要區別是:VST Streaming項目樣例使用輕質機制完成與主機之間的數據收發。它采用簡單的流控制器,支持基本觸發、連續和間斷流,以及溢出和下溢檢測。這些控制器 中斷信號源與目的地之間的2線握手信號,有效地選通數據流。控制器不支持全4線握手方案,該方案能夠調整上游節點或者被下游節點所調整;因此,系統特性化 以及確保這些流控制器控制的所有FIFO均能夠以要求的速率產生或消耗數據就落到了程序員的肩上。在VST Streaming項目樣例中通過簡單的更改默認情況下完成與主機之間的數據收發的FIFO,可以支持數據流傳輸到VST FPGA上的其他位置以進行進一步處理,或者通過PXI Express背板,利用P2P傳輸至其他模塊。

圖 14.FPGA流控制器和FIFO封裝實現基本流控制,并且能夠輕松改變數據流的源及目的地路線。

現在來看VST Streaming項目樣例的主機端,雖然機制與Simple VSA/VSG不同,也存在類似于儀器設計庫主機組件的集成,。VST Streaming項目樣例不使用LabVIEW類,而是將功能簡單地集成到子VI中,并將會話傳遞至子VI之間的寄存器總線。此寄存器總線會話還包含有 FPGA VI 引用,因此所有這些子VI不僅能夠訪問寄存器總線通信策略,而且還可以訪問NI-RIO FIFO和控制器。另外,不存在獨立的數據采集和生成會話;所有VI均使用同一會話。

圖 15.VST Streaming項目樣例主機接口具有一個基于寄存器總線的會話線,用于采集和生成subVI。在邏輯上,此樣例將采集和生成分組成為獨立的行,以方便閱讀。.

評論