NI矢量信號收發(fā)器的FPGA編程

圖 7. RF輸入回路以可配置I/Q速率生成已校準(zhǔn)數(shù)據(jù),并將其寫入DRAM。

RF輸出循環(huán)類似于RF輸入循環(huán),但是操作順序相反。來自DRAM的數(shù)據(jù)進(jìn)行內(nèi)插、定標(biāo)、頻移、相位校準(zhǔn)、內(nèi)插、校準(zhǔn),然后通過數(shù)模轉(zhuǎn)換器(DAC)生成。另外還有觸發(fā)和同步所用信號。

圖 8. RF輸出循環(huán)檢索來自DRAM的數(shù)據(jù)然后生成數(shù)據(jù)

過程子VI包含有循環(huán)和狀態(tài)機(jī),實(shí)現(xiàn)了多數(shù)據(jù)記錄采集和DRAM控制器對波形的排序。這些子VI包含了大量代碼,滿足了大帶寬和低滯后性能 要求,確保這些子VI能夠在全速率ADC數(shù)據(jù)轉(zhuǎn)換下溢出,以及產(chǎn)生全速率DAC數(shù)據(jù)而不發(fā)生下溢,同時仍然與主機(jī)之間進(jìn)行波形數(shù)據(jù)傳輸。

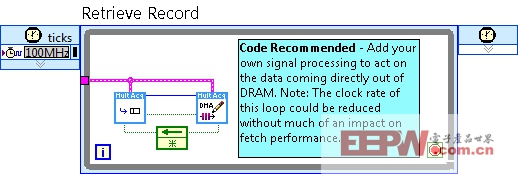

讀取循環(huán)實(shí)現(xiàn)的功能可以存在于多記錄采集過程之內(nèi),然而為了方便起見而將其顯示出來。該循環(huán)可以再數(shù)據(jù)離開DRAM時并在被發(fā)送到主機(jī)前進(jìn) 行數(shù)據(jù)處理。此路徑在它自己的回路之內(nèi),從而那些并不符合120 MHz RF輸入和輸出回路的定時要求的IP仍然可以使用。為了適應(yīng)這種IP,稍微降低此回路速率并不會影響讀取性能,然而如果降得過多,則只會增加數(shù)據(jù)到達(dá)主機(jī) 所需時間。這樣即使采樣內(nèi)存被填滿了,也不會丟失樣點(diǎn)或破壞數(shù)據(jù)。

圖 9.讀取循環(huán)提供了在已采集數(shù)據(jù)返回主機(jī)之前對其進(jìn)行處理的機(jī)會。在默認(rèn)情況下,讀取回路返回原始數(shù)據(jù)。

評論