基于DSP的自適應(yīng)數(shù)字抗噪聲模塊

關(guān)鍵詞: 數(shù)字信號處理(DSP);噪聲

概述

國內(nèi)目前第三代抗噪聲產(chǎn)品是利用動態(tài)降噪(DNR)技術(shù)。DNR技術(shù)是通過變化的話音峰值動態(tài)地調(diào)節(jié)輸出話音開關(guān),從而達(dá)到降噪的目的。它雖然是目前較好的一種抗噪聲模擬處理技術(shù),但也存在一些局限性,包括輕符音掉字和強音噪聲拖尾;降噪效果偏重于低頻;降噪完全采用硬件電路實現(xiàn),調(diào)試和維修比較麻煩等問題。由于存在這些問題,致使模擬DNR降噪產(chǎn)品的大量推廣應(yīng)用受到限制。隨著數(shù)字信號處理技術(shù)的迅速發(fā)展,以數(shù)字信號處理器及其相關(guān)算法為技術(shù)支撐的數(shù)字抗噪聲技術(shù)的產(chǎn)品不斷涌現(xiàn)。本文提出的數(shù)字抗噪聲模塊就是應(yīng)用現(xiàn)代數(shù)字信號處理(DSP)技術(shù)及其高速實時處理運算的特性,采用相應(yīng)的軟件算法,對高噪聲環(huán)境中的話音和噪音進(jìn)行處理,完成高噪聲環(huán)境中的語音通信功能。

本模塊的性能優(yōu)點包括:

a) 軟件采用自適應(yīng)濾波算法,數(shù)字抗噪聲處理器對噪聲的抑制量一般在50分貝以上,而且輸出話音平穩(wěn),無漏字和噪聲拖尾現(xiàn)象。

b) 數(shù)字抗噪聲處理器在整個話音頻帶內(nèi)(300~3000Hz)降噪量均衡。

c) 數(shù)字抗噪聲處理器可通過改變軟件算法滿足不同的抗噪聲要求,便于產(chǎn)品升級換代。

d)硬件成本比模擬DNR產(chǎn)品更低。

e)采用軟件加密技術(shù),產(chǎn)品不易被侵權(quán)、仿造,有利于保護(hù)生產(chǎn)廠家的利益。

主要指標(biāo)要求及總體解決思路

本數(shù)字抗噪聲處理模塊作為JK-DP10數(shù)字抗噪聲處理器的一部分,主要用于機載通信終端設(shè)備等噪聲環(huán)境中的通信聯(lián)絡(luò),其送話頻率范圍為300~3400Hz,平坦度不大于2dB。降噪性能為:模塊輸入端加入3mV、2秒斷續(xù)的正弦波信號(頻率依次為300Hz、700Hz、1000Hz、1500Hz、2000Hz、2500Hz、3000Hz)與加入3mV、120dB持續(xù)的白噪聲信號時,模塊輸出電平之差不小于50dB。

首先要選用一款合適的DSP器件。要求具有低功耗、高速數(shù)據(jù)運算和吞吐能力(40 MIPS以上),內(nèi)含A/ D、D/ A、Flash閃存(16KB)。然后建立有效的噪聲模型,設(shè)計自適應(yīng)濾波結(jié)構(gòu)及其相關(guān)軟件算法。接下來設(shè)計數(shù)字抗噪聲處理器的電磁兼容性(EMC),選用能適應(yīng)120dB環(huán)境噪聲的抗噪聲送話器器件。DSP硬件與相關(guān)軟件算法結(jié)合,使數(shù)字抗噪聲處理器在120dB高噪聲環(huán)境下,達(dá)到話音清晰度不小于98。

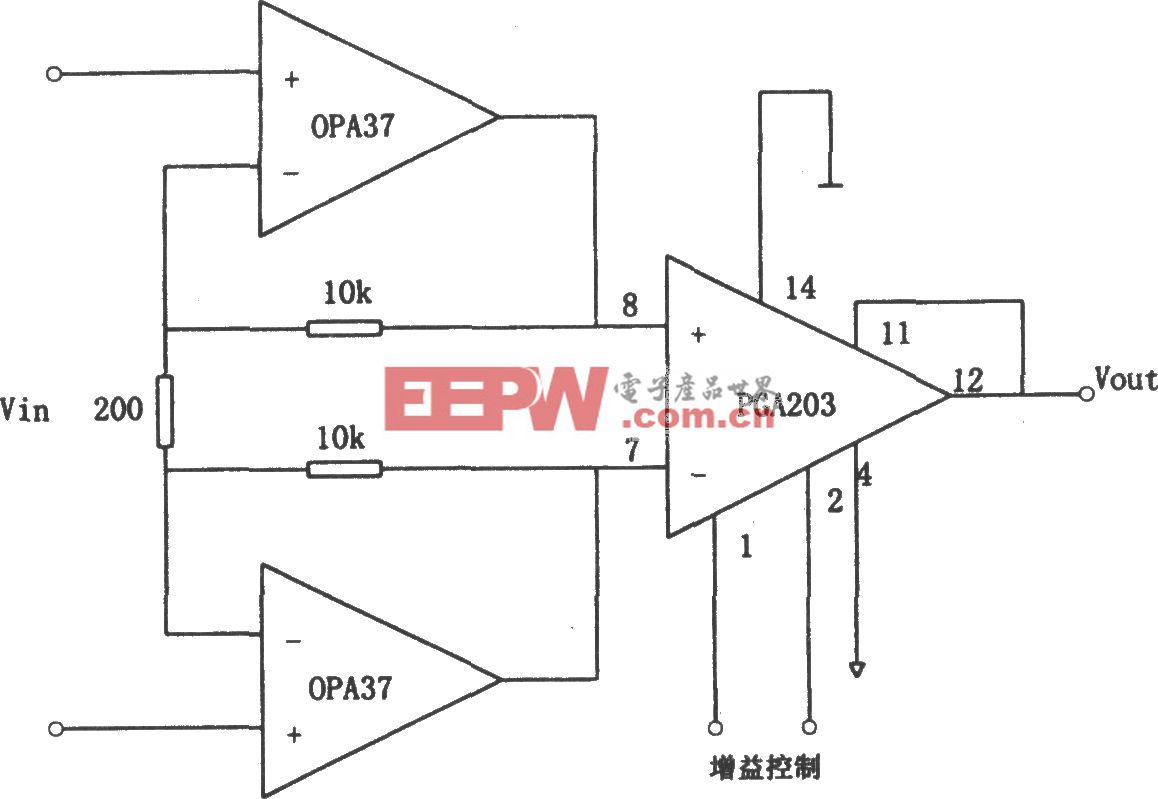

圖 1

軟硬件設(shè)計方案

主要工作原理

本處理器主要完成高噪聲環(huán)境下話音的高清晰度通信功能。話音信號和環(huán)境噪聲通過MIC輸入到前置放大級,前置放大級的作用是把話音和環(huán)境噪聲放大到專用DSP芯片內(nèi)的A/D能識別的幅度,以便A/D能正常轉(zhuǎn)換信號,模擬信號通過A/D轉(zhuǎn)換后變成12位的數(shù)字信號進(jìn)入DSP的運算單元,DSP在前3秒鐘內(nèi)完成測試周圍環(huán)境噪聲的大小并建立數(shù)學(xué)模型,然后按給定的算法處理話音和噪聲,把處理結(jié)果通過數(shù)據(jù)總線送到D/A,經(jīng)平滑濾波后送入后級放大器,后級放大器的作用是為了滿足關(guān)聯(lián)設(shè)備輸入要求。

DSP芯片選擇

本文設(shè)計的JK—DP10數(shù)字抗噪聲處理器對數(shù)字信號處理器芯片的要求較高。芯片既要有很強的實時處理性能,又要有很高的運算速度和數(shù)據(jù)吞吐能力;還要求功耗低,外部的A/ D、D/ A及Flash閃存最好集成在DSP內(nèi)部,以減小產(chǎn)品體積。所以,選用TMS320C5XX系列DSP芯片中的一款作為處理芯片,外配高速A/ D、D/ A及32KB Fl a s h作程序加載。

軟件算法方案

數(shù)字抗噪聲處理器是由自適應(yīng)濾波器來實現(xiàn)的。自適應(yīng)濾波器具有跟蹤信號和噪聲變化的能力,使濾波器的特性也隨信號和噪聲的變化而變化,以達(dá)到最優(yōu)濾波效果。

自適應(yīng)濾波器的特性變化是由自適應(yīng)算法通過調(diào)整濾波器權(quán)系數(shù)來實現(xiàn)。一般情況,自適應(yīng)濾波器由兩部分組成,一是濾波器結(jié)構(gòu),二是調(diào)整濾波器系數(shù)的自適應(yīng)算法。自適應(yīng)濾波器的結(jié)構(gòu)采用FIR結(jié)構(gòu)。對帶內(nèi)白噪聲的處理用經(jīng)典的LMS算法還不能達(dá)到最優(yōu)的降噪效果,還要利用噪聲的自相關(guān)特性和功率譜密度特性,在LMS算法的基礎(chǔ)上作適當(dāng)修整才能達(dá)到最佳的降噪效果。

數(shù)字式抗噪聲送話器組的DSP實現(xiàn)結(jié)構(gòu)如圖1所示。

原始輸入信號d(n)包括信號和噪聲,x(n)為參考噪聲輸入。這種自適應(yīng)濾波器實質(zhì)上是完成d(n)中的噪聲估計,并把估計值y(n)與原始信道相減以達(dá)到噪聲消除的結(jié)果,當(dāng)然,估計值y(n)與原始輸入信號并不是簡單的代數(shù)相減,而是有一套相應(yīng)的軟件算法,如相關(guān)功率的功率譜分析等。

圖1中,自適應(yīng)濾波器采用橫向型結(jié)構(gòu),濾波器的輸出y(n)表示為:

N- 1

y(n)= ∑ Wi (n- i)

i =0

N為濾波器的階數(shù)。

軟件設(shè)計

一個自適應(yīng)濾波器實現(xiàn)的復(fù)雜性通常是由它所需要的乘法次數(shù)和階數(shù)來衡量。基于DSP實現(xiàn)的自適應(yīng)濾波器系統(tǒng),其DSP芯片的數(shù)據(jù)吞吐量和數(shù)據(jù)處理速度也相當(dāng)重要。本數(shù)字抗噪聲處理器采用了120階自適應(yīng)數(shù)字濾波器,選用了運算速度為40MIPS的DSP芯片作為主處理器,由于該DSP芯片內(nèi)包含A/ D和D/ A及16KB的f l a s h存儲器,這些片內(nèi)資源使自適應(yīng)濾波器的實現(xiàn)更有效。

根據(jù)噪聲的自相關(guān)特性和功率密度性,軟件上除采用了傳統(tǒng)對稱橫向結(jié)構(gòu)的FIR濾波器中的LMS算法外,還對噪聲和信號的功率譜密度進(jìn)行估計,即對采樣編碼的16個值進(jìn)行平方累加,求出其平均功率值,與前一樣點功率值進(jìn)行比較,比較后的差值與設(shè)定的噪聲門限值進(jìn)行相除,結(jié)果若大于1,則調(diào)整濾波器的權(quán)系數(shù)變小,信號輸出幅度變大,若結(jié)果小于等于1,則濾波器的權(quán)系數(shù)變大,信號輸出幅度變小。

定制專用抗噪聲DSP芯片

調(diào)試工作完成后,交給專門制作DSP芯片的公司作成一片具有抗噪聲功能的DSP專用芯片。經(jīng)過實測,整機的耗電不大于70mA,DSP芯片的引出腳縮減到64引腳,大大減小了印刷電路板的面積。由于軟件代碼一次性掩膜在芯片內(nèi),免去了每次都寫入代碼的麻煩,減少了調(diào)試的工作量。一般情況下,模塊只要調(diào)試3個點就可完成,大大降低了調(diào)試成本,有利于批量生產(chǎn)。

結(jié)語

數(shù)字抗噪聲模塊使用DSP芯片,利用自適應(yīng)技術(shù),既提高了通信產(chǎn)品的抗噪性能,又降低了生產(chǎn)成本。該模塊已成功應(yīng)用于我國機載通信設(shè)備。■

參考文獻(xiàn)

1 何振亞.數(shù)字信號處理技術(shù).東南大學(xué)出版社.

2 “TMS320C54X DSP Reference Set Volume 1:“CPU and Peripherals”,Texas Instruments ,1997

評論