什么是PCI總線?其接口芯片的應(yīng)用

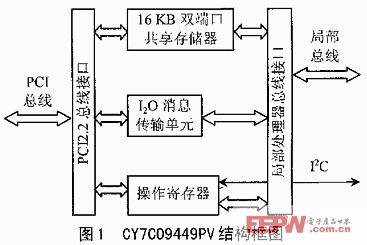

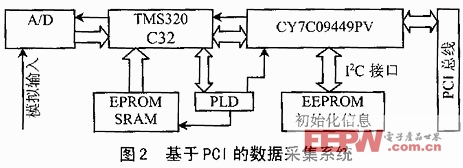

PCI (Peripheral Component Interconnect)總線是一種高性能局部總線,是為了滿足外設(shè)間以及外設(shè)與主機間高速數(shù)據(jù)傳輸而提出來的。在數(shù)字圖形、圖像和語音處理,以及高速實時數(shù)據(jù)采集與處理等對數(shù)據(jù)傳輸率要求較高的應(yīng)用中,采用PCI總線來進行數(shù)據(jù)傳輸,可以解決原有的標準總線數(shù)據(jù)傳輸率低帶來的瓶頸問題。 1 PCI局部總線特點 * 傳輸率高:在33MHz的時鐘頻率下,對于32位的PCI總線,峰值數(shù)據(jù)傳輸可以達到132MB/s;64位的PCI總線可達264MB/s。對于64位的66MHz時鐘的PCI總線,可以達到528MB/s,遠遠大于標準ISA的5MB/s和EISA的33MB/s傳輸率。 *線性突發(fā)傳輸:減少了地址操作,更有效地利用總線的帶寬來傳輸數(shù)據(jù),可以確保總線滿載數(shù)據(jù)。 *采用獨立于處理器的結(jié)構(gòu):圖為PCI總線開發(fā)的設(shè)備是針對PCI的,不受處理器的限制,所以PCI設(shè)備的設(shè)計獨立于處理器的升級。 *自動配置功能:每個PCI設(shè)備有256字節(jié)的配置寄存器,可以實現(xiàn)設(shè)備的即插即用。 *軟件透明:在與PCI設(shè)備通信時,軟件驅(qū)動程序使用相同的命令集和狀態(tài)定義。 2 PCI接口的兩種設(shè)計方法 PCI 接口的設(shè)計必須符合PCI總線規(guī)范定義的電氣特性和時序要求。有兩種PCI接口的實現(xiàn)方案:使用可編程邏輯器件(FPGA或CPLD)和專用PCI接口芯片。使用可編程邏輯器件,可以選擇實現(xiàn)部分PCI規(guī)范的一個子集,這種方法比較靈活,但開發(fā)難度大,開發(fā)周期長。采用專用PCI接口芯片,可以縮短開發(fā)周期,降低開發(fā)難度。 3 CY7C90449PV介紹 CY7C09449PV 是Cypress公司推出的PCI主/從接口芯片,符合PCI2.2規(guī)范,可以直接與很多微處理器進行無縫連接。CY7C9449V提供16KB的雙端口共享存儲器(SRAM),用來在PCI總線和局部處理器間傳輸數(shù)據(jù);I2O消息傳輸單元具有4個32位FIFO,用來實現(xiàn)消息隊列和中斷功能;局部總線時鐘最大50MHz,單一3.3V電源供電;對3.3V和5V的PCI信號兼容,使用160引腳的TQFP封裝。 3.1 CY7C09449PV結(jié)構(gòu) CY7C09449PV的結(jié)構(gòu)如圖1所示。 3.2 功能模塊介紹 CY7C09449PV 提供64字節(jié)的PCI頭標區(qū)配置寄存器空間。其中Vender ID、Device ID、Revision ID、;Header Type、Class Code用于設(shè)備的識別。命令寄存器(Command)包含設(shè)備控制位,包括允許存儲器讀寫響應(yīng)、I/O讀寫響應(yīng)等。狀態(tài)寄存器(Status)用于記錄 PCI總線相關(guān)事件的狀態(tài)信息。基址寄存器0(BAR0)提供設(shè)備在PCI存儲空間起始地址,31~15可讀寫,通知系統(tǒng)BIOS此設(shè)備所要求的PCI存儲空間為32KB,任何對31~15位與BAR0相符合的PCI存儲空間訪問的,CY7C09449PV都會影響并接受傳輸。基址寄存器1(BAR1)是 CY7C09449PV的I/O指針空間的地址。 CY7C09449PV 提供PCI總線接口、局部處理器總線接口和I2C串行EEPROM接口,以及內(nèi)部16KB雙端口SRAM、I2O消息傳輸單元和控制寄存器。數(shù)據(jù)的傳輸可以在PCI總線和局部處理器總線間進行。PCI總線和局部總線都能通過操作寄存器對I2C接口進行操作。 PCI 總線和局部處理器總線間可以通過共享的雙端口存儲器進行數(shù)據(jù)交換。由于共享存儲器是“臨界資源”,CY7C09449PV在仲裁寄存器(CRB_FLAGS)中,為PCI總線和局部處理器部各提供了4個仲裁檔志位(L0,P0,L1,P1,L2,P2,P3,P3),來對共享存儲器進行并發(fā)互斥訪問。對了實現(xiàn)線性突發(fā)傳輸,提供了DMA控制寄存器,PCI總線和局部處理器總線都能通過DMA控制寄存器,來啟動突發(fā)傳輸。為了保證對DMA 控制器的互斥訪問,DMA控制寄存器也提供了仲裁標志位。CY7C09449PV為局部處理器提供了一個映射到整個PCI地址空間的8KB存儲器窗口。通過這個窗口,局部處理器可以不經(jīng)過共享存儲器,直接對PCI地址空間進行訪問,直接訪問寄存器(DAHBASE)負責(zé)對這個窗口的操作。 CY7C09449PV的I2O消息傳輸單元具有符合智能I/O(Intelligent I/O)1.5規(guī)范的消息隊列和斷功能,由4個深度為32的32位FIFO(Inbound Free/Post,Outbound Free/Post)和共享存儲器來實現(xiàn)。這4個FIFO也能用作通用FIFO。 PCI總線和局部處理器間的消息也能通過郵箱來傳輸。主機通過寫Host to Local Data Mailbox(HLDATA)郵箱寄存器,向局部處理器傳送消息數(shù)據(jù),并產(chǎn)生中斷標志位,等局部處理器讀取消息數(shù)據(jù)后,中斷標志位自動復(fù)位。局部處理器能通過寫(Local To Host Data Maibox)郵箱寄存器,向主機發(fā)送消息數(shù)據(jù),并產(chǎn)生中斷標志位。主機讀取消息數(shù)據(jù)后,標志位自動復(fù)位。 通過I2C接口連接EEPROM,可以保存CY7C09449PV的初始化數(shù)據(jù)。這些數(shù)據(jù)包括PCI總線和局部處理器總線的配置信息。在復(fù)位完成后, PY7C09449PV在響應(yīng)PCI總線和局部總線交易以前自動下載這些數(shù)據(jù),進行初始化操作。通過I2C控制寄存器組可以對I2C端口進行讀寫。I2C 控制寄存器組包括3個寄存器:I2C命令寄存器(NVCMD)、I2C讀數(shù)據(jù)寄存器(NVREAD)、I2C狀態(tài)寄存器(NVSTAT)。 CY7C09449PV 的中斷控制器為PCI總線和局部處理器總線分別提供了獨立的中斷掩碼和命令/狀態(tài)寄存器:HINT(主機中斷控制和狀態(tài)寄存器)、LINT(局部處理中斷控制和狀態(tài)處理器)。中斷源有:DMA完成、郵箱、FIFO非空、FIFO溢出等,以及1個外部中斷引腳。內(nèi)部資源如表1所列。 4 基于PCI與C32數(shù)據(jù)采集系統(tǒng)的設(shè)計方案 C32是一種32位的浮點DSP,具有較高的性價比,在實時數(shù)據(jù)采集與高速信號處理中得到了廣泛的應(yīng)用。使用CY7C09449PV作為接口芯片,可以實現(xiàn)PCI總線與基于C32的DSP系統(tǒng)的連接。 將CY7C09449PV 的RSTOUTD引腳與C32的復(fù)位信號相連,可以實現(xiàn)主機對C32進行復(fù)位。I2C接口引腳要接2.2KΩ到10kΩ的上位電阻。接口輸入引腳在不用時,要上拉到高電平或接地。圖2中的PLD實現(xiàn)C32對CY7C9449PV和A/D轉(zhuǎn)換器的片選,以及C32的復(fù)位BOOT LOADER所需的信號邏輯。EPROM存儲C32程序,SRAM存放數(shù)據(jù)和運行時的程序,EEPROM存入CY7C09449PV的初始化信息。 系統(tǒng)結(jié)構(gòu)如圖2所示。 采集到的數(shù)據(jù)有兩種方案進行傳輸,使用FIFO或DMA。FIFO傳輸可以保證順序的傳輸,但傳輸效率低,適用于速率要求較低的應(yīng)用。使用DMA進行傳輸,能充分利用PCI總線PCI總線的突發(fā)傳輸能力,適用于對傳輸率要求較高的情況。共享存儲器分為模塊A和模塊B。DSP先把采集到的數(shù)據(jù)寫入模塊A,等數(shù)據(jù)寫滿后,啟動模塊A的DMA傳輸;同時將接下來采集到的數(shù)據(jù)寫入模塊B,等模塊B數(shù)據(jù)裝滿后,啟動模塊B的DMA傳輸,這樣循環(huán)下云,可以使數(shù)據(jù)的采集和DMA傳輸并行進行。

表1 CY7C9449PV內(nèi)部資源存儲映射存儲模塊 偏移地址[14:0] 大小/KB I2O寄存器

操作寄存器

保留空間

PCI直接訪問窗口

共享雙端口存儲器0x0000-0x03FF

0x4000-0x07FF

0x0800-0x1FFF

0x2000-0x3FFF

0x4000-0x7FFF1

1

6

8

16

評論