解析在PCB設計中采用時間交替超高速模數轉換器

采用時間交替模數轉換器(ADC),以每秒數十億次的速度采集同步采樣模擬信號,對于設計工程師來說,這是一項極大的技術挑戰,需要非常完善的混合信號電路。時間交替的根本目標是通過增加轉換器,在不影響分辨率和動態性能的前提下使采樣頻率增倍。

本文探討時間交替模數轉換器的主要技術難點,并提供切實可行的系統設計指導,包括可解決上述問題的創新性元件功能和設計方法。本文還提供從7Gsps雙轉換器芯片“交替解決方案”測得的FFT結果。最后,文章還描述了實現高性能所需的應用支持電路,包括時鐘源和驅動放大器。

對更高采樣速度的需求不斷增加

何時提高采樣頻率會更加有益,其中的原因又是什么呢?這個問題有多種答案。模數轉換器的采樣速度基本上直接決定了可以在一個采樣瞬間進行數字化的瞬時帶寬。尼奎斯特和香農采樣定理證明了最大可用采樣帶寬(BW)相當于采樣頻率Fs的一半。

3GSPS模數轉換器實現了在一次采樣期內采集1.5GHz模擬信號頻譜。如果采樣速度翻倍,尼奎斯特帶寬也倍增至3GHz.通過時間交替實現采樣帶寬倍增對于很多應用來說都是有益的。例如,無線電收發器架構可以增加信息信號載波數,從而增加系統數據輸出量。采樣頻率倍增還可以提高采用飛行時間(TOF)原理的LIDAR測量系統的分辨率。實際上,通過縮短有效采樣期可以降低飛行時間測量值的不確定性。

數字示波器還需要高采樣頻率Fs/輸入頻率FIN比值,以準確采集復合模擬或數字信號。要采集輸入頻率的諧波部分,就要求采樣頻率必須是輸入頻率(最大值)的倍數。例如,如果示波器采樣頻率不夠高,且更高階諧波位于模數轉換器的尼奎斯特帶寬外,方形波將顯示為正弦形。

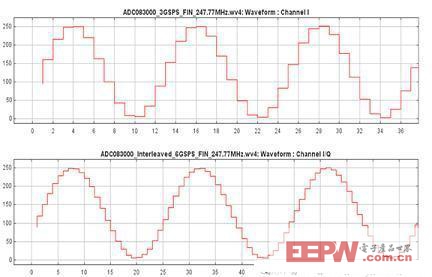

圖1說明了示波器前端雙倍采樣頻率的益處。6GSPS采樣波形是采樣模擬輸入更準確的表示形式。很多其他測試儀器系統(例如質譜儀和伽馬射線望遠鏡)依靠較高的過采樣/FIN進行脈沖波形測量。

圖1:以3GSPS和6GSPS采樣的247.77MHz信號的時域值圖。

增加采樣頻率還具有其他優點。過采樣信號還實現了通過數字濾波在數字域改善增益的特點。實際上,模數轉換器噪聲底可在更大輸出帶寬上擴散。倍增固定輸入帶寬的采樣率在動態范圍使噪聲改善了3dB.采樣頻率每倍增一次,將為動態范圍提供一個附加3dB.

時間交替技術的難點

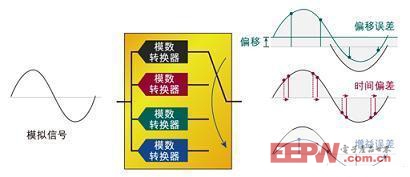

時間交替的主要難點是通道間采樣時鐘邊沿的精確校準和IC間固有變化的補償。精確匹配各單獨模擬數據轉換器間的增益、偏移和時鐘相位是一項很大的挑戰,主要因為這些參數都取決于頻率。除非能夠實現這些參數的精確匹配,否則動態性能和分辨率將會降低。圖2顯示了三個主要誤差源。

圖2:交替模數轉換器產生的增益、偏移和時間誤差。

采樣時鐘相位調整

通常,雙通道交替轉換器系統需要模數轉換器輸入采樣時鐘的時間移動1/2個時鐘周期。但是,ADC083000結構使用芯片內交替,其時鐘頻率等于采樣率的一半,即3GSPS的時鐘頻率為1.5GHz.因此,對于采用兩個ADC083000的雙通道系統,模數轉換器輸入采樣時鐘邊沿必須移動1/4個時鐘周期或錯開90(。即1.5GHz時鐘對應于166.67ps.

可以相對準確地計算出對應1/4時鐘周期相移的時鐘信號走線長度。對于FR4印刷電路板材料,信號以20cm/ns(即50ps為1cm)的速度傳播。例如,如果傳輸到一個模數轉換器的時鐘走線比另一個長3cm,這將產生150ps的相移。難點在于精確符合附加的16.67ps時移。

ADC083000具有集成的時鐘相位調整功能,使用戶可以向輸入采樣時鐘添加延時,以相對于另一模數轉換器的采樣時鐘實現相移。可以通過SPI總線,采用兩個內部寄存器手動調整模數轉換器的時鐘相位。只能沿一個方向實現相移,增加延時。設計工程師應確定兩個分立模數轉換器中的位置,確定哪一個“在前”并調整其相位,使其采樣邊沿與另一模數轉換器采樣邊沿呈90o,從而可實現亞皮秒調整分辨率。

通道間增益和偏移匹配

在雙轉換器交替系統中,通道增益失配產生的誤差電壓會導致Fs/2-FIN和Fs/4±FIN發生圖像雜散信號(假設輸入信號在第一尼奎斯特頻帶內)。8位轉換器具有28或256個編碼。假設轉換器全輸入范圍為Vp-p,,LSB大小等于1V/256=3.9mV.我們可以得出1/2LSB精確度需要的增益匹配為0.2%.

ADC083000的輸入全范圍電壓或增益可以使用9位數據分辨值進行線性且單調的調整。調整范圍是標稱700mVp-p差分值的±20%,或560mVp-p至840mVp-p.

840mV-560mV=280mV.

29=512步幅

280mV/512=546.88μV

此微調允許比上述要求大0.2%的增益匹配。

相鄰通道間的偏移失配將產生誤差電壓,導致Fs/2處發生偏移雜散信號。由于偏移雜散信號位于尼奎斯特頻帶邊沿,雙通道系統的設計人員通常可以據此計劃系統頻率,并著力于增益和相位匹配。

但是,假設需要的偏移匹配也是1/2LSB,ADC083000的輸入偏移可以使用9位分辨率從標稱零偏移線性且單調的調整為45mV偏移。因此,每個編碼步幅提供0.176mV偏移,9位分辨率實現1/2LSB精確度。

數字輸出的同步化

從兩個模數轉換器輸出的數據流同步化對于實現優異采樣速度和帶寬組合至關重要。也就是說,如果各轉換器間未實現輸出同步,就無法采集有意義的數據。千兆采樣率模數轉換器可多路分離輸出數據,以降低數字輸出數據傳輸率。用戶可以選擇使數據傳輸率分離為1/2或1/4,這取決于采用的FPGA技術的處理能力。

輸出采集時鐘(DCLK)也被分離,可在SDR或DDR模式中配置。但是,多路分離帶來新的考量問題,因為現在增加了輸入采樣時鐘和各模數轉換器DCLK輸出之間的協調不確定性。為了克服這個問題,ADC083000可以精確復位采樣時鐘輸入與DCLK輸出的關系,這由用戶提供的DCLK_RST脈沖確定。這允許一個系統中采用多個模數轉換器,使其DCLK(和數據)輸出在與采樣共享輸入時鐘相同的時間點躍遷,從而實現多個模數轉換器之間的同步。

評論