基于DSP Builder的FIR濾波器的設計與實現

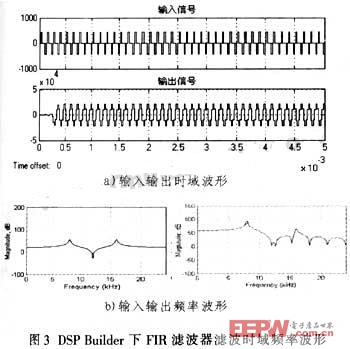

輸入信號分別采用頻率f1=8KHz和f2=16KHz的兩個正弦信號進行疊加。其中的仿真波形如圖3所示,從FIR濾波電路的仿真結果看出,輸入信號通過濾波器后輸出基本上變成單頻率的正弦信號,進一步通過頻譜儀可看出f2得到了較大的抑制,與條件規定的fc=10.8kHz低通濾波器相符合,至此完成了模型仿真。

在Simulink中進行的仿真是屬于系統驗證性質的,是對MDL文件進行的仿真,并沒有對生成的VHDL代碼進行過仿真。事實上,生成VHDL描述是RTL級的,是針對具體的硬件結構的,而在Matlab的Simulink中的模型仿真是算法級(系統級)的,是針對算法實現的,這二者之間有可能存在軟件理解上的差異,轉換后的VHDL代碼實現可能與MDL模型描述的情況不完全相符,這就是需要針對生成的RTL級VHDL代碼進行功能仿真。

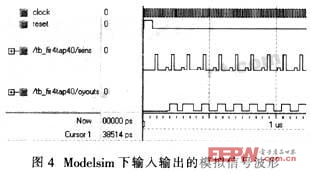

在此,筆者利用Modelsim對生成的VHDL代碼進行功能仿真。設置輸入輸出信號均為模擬形式,出現如圖4所示的仿真波形,可以看到這與Simulink里的仿真結果基本一致,即可在QuartusⅡ環境下進行硬件設計。

在QuartusⅡ環境中打開DSPBuilder建立的QuartusⅡ項目文件firl.qpf。在QuartusⅡ中進行再一次仿真,由此可以看到符合要求時序波形,然后指定器件引腳并進行編譯,最后下載到FPGA器件中,就可以對硬件進行測試,加上CLCOK信號和使能信號,用信號發生器產生所要求的兩個不同頻率的正弦信號,就可以在示波器上看到濾波以后的結果,需要設計不同的濾波器電路時,僅修改FIR濾波模型文件就可以實現,這樣不僅避免了繁瑣的VHDL語言編程,而且便于進行調整。

5 結束語

在利用FPGA進行數字濾波器的開發時,采用DSPBuilder作為設計工具能加快進度。當然,在實際應用中,受精度、速度和器件選擇方面的影響,可以對其轉化的VHDL進行進一步的優化。

評論