基于FPGA和DSP組合的無線基站

FPGA和DSP之間的“智能配分”可使無線系統(tǒng)設(shè)計師獲得最佳性能組合和成本——效能。應(yīng)用DSP和FPGA組合可使成本降低。對于無線基站,組合有DSP可編程邏輯的系統(tǒng)配分,可促使更大的產(chǎn)品設(shè)計和市場成功率。

更高數(shù)據(jù)率的需求正在驅(qū)使無線蜂窩系統(tǒng)從窄帶2G GSM,IS-95系統(tǒng)到W-CDMA基3G和3.5G系統(tǒng)(支持高達10Mbps峰值數(shù)據(jù)率)變革。將來,3Gpp遠期變革規(guī)范面向復(fù)雜的信號處理技術(shù),如多輸入多輸出(MIMO)以及新的無線電技術(shù)(如正交頻分多址OFDMA,多載波碼分多址MC-CDMA)。這些技術(shù)對于實現(xiàn)超過吞吐量100Mbps的目標起關(guān)鍵作用。

另外的OFDM基寬帶無線系統(tǒng),如WiMAX現(xiàn)在傳輸速度超過70Mbps。靠較高級的調(diào)制技術(shù)和變速率信道編碼可以實現(xiàn)數(shù)據(jù)率的改善。復(fù)雜的空間信號處理方法(包括聚束和MIMO無線技術(shù))也是增加數(shù)據(jù)率的辦法。然而,這種技術(shù)對基站設(shè)計師所產(chǎn)生的問題是:需要可縮放性、成本、效率和跨越多個標準的靈活性。

多可變目標

無線系統(tǒng)設(shè)計師需要滿足大量關(guān)鍵技術(shù)要求,包括處理速度、靈活性、產(chǎn)品上市時間。所有這些要求決定對硬件平臺的選擇。主要的變量包括處理帶寬、靈活性和降低成本的路徑。

處理帶寬

WiMAX與W-CDMA和CDM2000蜂窩系統(tǒng)相比,明顯地具有較高的吞吐量和數(shù)據(jù)要求。為了支持這些較高的數(shù)據(jù)率,基礎(chǔ)硬件平臺必須具有寬處理帶寬。另外,幾種先進的信號處理技術(shù),如快速傅里葉變換/快速傅里葉逆變換(FFT/IFFT)、聚束、MIMO、波峰因數(shù)縮減(CFR)、數(shù)字預(yù)失真(DPD)都是計算密集的,需要每秒幾百萬乘和累加運算。

靈活性

WiMAX是一個相當(dāng)新的市場,現(xiàn)正處于開發(fā)和采用階段。現(xiàn)在仍然不清楚在這很多移動寬帶技術(shù)(WiMAX,Wibrow,Super3G,LTE,Ultra3G等)中,哪一種將被大量采用。

現(xiàn)在,末端產(chǎn)品靈活性和可編程性對多協(xié)議基站是關(guān)鍵性的。

降低成本的路徑

對于OEM和服務(wù)供應(yīng)商來講,為了保持競爭力,最終產(chǎn)品的成本比靈活性更重要。在樣機設(shè)計階段選擇正確的硬件平臺,為生產(chǎn)制造提供無縫降低成本的路徑,這會節(jié)省上百萬工程成本。否則,需要重新設(shè)計系統(tǒng)。

系統(tǒng)結(jié)構(gòu)的邏輯任務(wù)分配

控制、信號處理和數(shù)據(jù)通路運行構(gòu)成無線基站中處理負載的主體。實現(xiàn)這些功能的最通用方法是采用微控制器(MCU)、FPGA和可編程DSP的組合。MCU控制系統(tǒng)、而FPGA和DSP控制數(shù)據(jù)流處理。DSP軟件實現(xiàn)系統(tǒng)的輕載處理要求和定向控制任務(wù)。重載最好的實現(xiàn)方法是用FPGA,因為FPGA具有很強的并行處理能力。

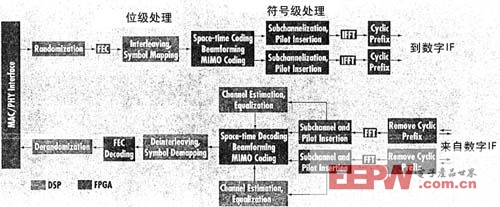

組合的DSP和FPGA確保整個系統(tǒng)的靈活性,并提供重新可編程性以確定系統(tǒng)缺陷,而且支持不同的標準。DSP和FPGA之間的分配策略依賴于處理要求、系統(tǒng)帶寬、系統(tǒng)配置、發(fā)射和接收天線數(shù)。圖1示出OFDMA基系統(tǒng)(如WiMAX或LTE)中基帶物理層(PHY)功能的典型DSP/FPGA分配。

圖1 OFDMA系統(tǒng)中DSP/FPGA分配

包含先進的多天線技術(shù),這類系統(tǒng)所提供的吞吐量可達到75~100MPS。基帶PHY功能可大致分為位級(bit-level)處理和符號級(Symbol-level)處理功能。

位級處理

位級處理單元包括發(fā)射端的隨機化、前向糾錯(FEC)、到四相相移鍵控(QPSK)和正交調(diào)幅(QAM)功能的交織和變換。相應(yīng)的接收處理位級單元包括符號解變換、解交織、FEC解碼和解隨機性。

除FEC譯碼外的所有位級功能都是相當(dāng)簡單的,而且計算不是密集的。例如,隨機性包含數(shù)據(jù)位的模2加法(借助簡單偽隨機二進制時序產(chǎn)生器輸出)。盡管FPGA比固定總線寬度的DSP能為位級處理提供更大的靈活性。但是,低計算復(fù)雜性允許DSP處理這些功能。相比,F(xiàn)EC譯碼包括Viterbi譯碼、Turbo卷積譯碼、Turbo乘積譯碼和LDPC譯碼是計算密集的,而且DSP處理時會消耗有效帶寬。

FPGA廣泛用于卸載這些功能。同樣FPGA也可用到MAC層的接口,以實現(xiàn)一定的較低MAC功能(如加密/解密和鑒別)。

評論