基于DSP片外高速海置SDRAM存儲系統設計

3.2 06201 EMIF SDRAM寄存器設置

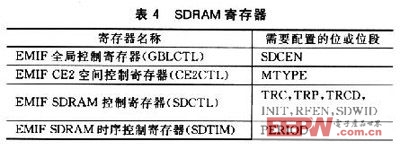

表4列出了配置SDRAM需要設置的EMIF寄存器名稱及相應的位或位段。

EMIF全局控制寄存器中的SDCEN位(位6)設置為1,用來使能SDRAM同步時鐘SDCLK的輸出。EMIFCE2空間控制寄存器中的MTYPE位段(位6~4)設置為011b,用來配置CE2為32位寬的SDRAM空間。由IS42S16400數據手冊可查得tRC=70 ns、tRp=18 ns、tRCD=18 ns,故而EMIF SDRAM控制寄存器中的TRC位段(位15~12)應設置為0110b,TRP位段(位19~16)應設置為0001b,TRCD位段(位23~20)應設置為0001b。INIT位(位24)置1,用來強制對SDRAM進行上電初始化。RFEN位(位25)置1,用來使能EMIF對SDRAM的刷新。SDWID位(位26)置1,用來向EMIF表明所使用的SDRAM芯片的字寬為16位。由于IS42S16400的刷新頻率為每64 ms 4096次,故根據公式PERIOD=trefesh/tcyc,EMIF SDRAM時序控制寄存器中的PERIOD位段(位11~O)被設置為0x61A。

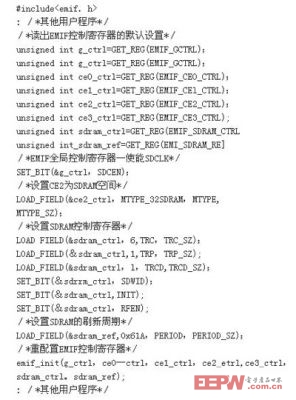

3.3 CCS開發環境中SDRAM配置程序源代碼

TI公司的集成開發環境CCS(Code Composer Studio)中,IS42S16400SDRAM芯片的配置程序C代碼如下:

結 語

以上介紹了TMS320C6201 DSP芯片與SDRAM(IS42S16400)的具體硬件接口實現。由于SDRAM具有的大容量、高速度和低價格的優勢,使用SDRAM構建嵌入式應用海量存儲系統會成為一種行之有效的方法。目前該系統已調試完畢。使用SDRAM作為DSP系統外接高速、大容量主存儲器具有非常明顯的優勢,充分顯示了SDRAM在嵌人式系統中的良好應用前景。

評論