基于FPDP和VME總線的多DSP通用并行處理系統設計方案

3.3 電路靈活配置

3.3.1 JTAG接口菊花鏈設計

TMS320C6701備有基于IEEE 1149.1標準的邊界掃描測試接口,從而為設計人員提供了一個實時的硬件仿真與調試環境。由于處理機是一個有4個DSP的多DSP系統,我們將DSP的JTAG接口與14 pin Header間以菊花鏈方式互連。按照JTAG口驅動能力的要求,我們將關鍵信號通過一個緩沖器進行增強。

3.3.2 DSP中斷信號分配

多DSP系統不可避免會產生DSP中斷信號不夠用的問題。在處理機的設計過程中,我們分別將三個從DSP和FPDP/RM端口的中斷請求信號引至主DSP的附屬邏輯CPLD中進行統一分配。在CPLD中設定一個控制寄存器,外掛于主DSP的EMIF下。當主DSP接收到中斷請求后,它通過CPLD控制寄存器標示分析中斷信號的來源,從而正確響應。

4、結論

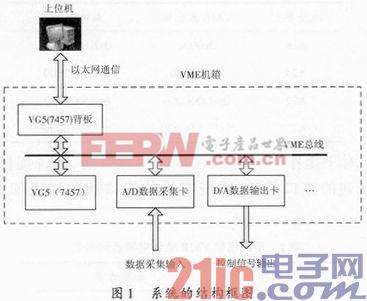

采用混合總線模式的設計方法將大大提高數字信號處理系統的并行處理和數據傳輸能力。本文采用FPDP總線傳輸協議,實現了多總線子板間信號高速傳輸。最大為160MB/S的數據傳輸帶寬,完全滿足板間DSP芯片點對點通信的需求。同時,采用VME總線完成上下位機程序下載和數據監控,提高了系統的穩定性和可靠性。

本文設計的基于FPDP和VME雙總線的高速實時信號處理多子板系統,目前在水下通信領域已取得成功應用。詳細介紹的系統核心子板——多DSP通用并行處理機基于一主三從的多處理器結構,不僅可以多板多模式工作,也可以單板使用。目前在DSP大規模并行技術向片間發展的主流下,雖然文中的DSP器件以TMS320C6701為例,但系統結構對其他DSP器件構成的多DSP并行處理系統設計都具有一定的參考價值。

評論