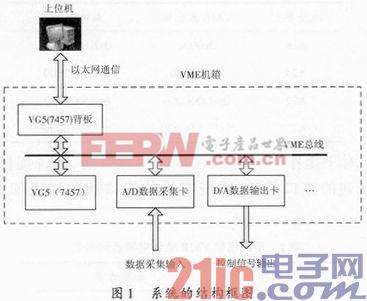

基于FPDP和VME總線的多DSP通用并行處理系統設計方案

3、并行處理系統板極設計

3.1 單板結構及功能描述

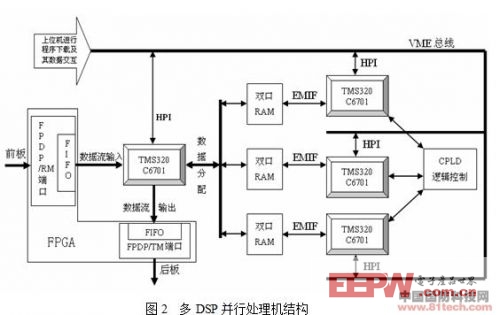

本文介紹的高速實時信號處理系統,其核心子板是多DSP并行處理機。它包括多DSP模塊、VME總線模塊和FPDP總線模塊。DSP選用TMS320C6701芯片,它是TI公司第一代采用VelociTITM高性能超長指令字結構的高性能32位浮點型數字型號處理器,其運行時鐘頻率最高可達167MHz,峰值處理速度可以達到1GFLOPS和34MMACS的運算能力。

它主要包括C6701、SDRAM、FLASH、雙口RAM、數據地址緩沖以及DSP附屬的邏輯控制CPLD和實現兩類總線協議的FPGA芯片。

多DSP并行處理系統設計的核心是實現多DSP之間的通信控制及數據交換。DSP之間的互連結構分為共享總線或共享存儲器的緊耦合連接方式和擁有各自獨立的數據存儲器而通過通信口相連的松耦合連接方式。緊耦合連接方式限制整個系統節點數目的規模,從而降低系統的擴展性。因此,我們采用松耦合連接方式,通過雙口RAM實現一主三從DSP之間的通信控制及數據交換。

VME和FPDP總線協議我們采用FPGA芯片實現。VME總線主要用于各個DSP的HPI口與上位機通訊。DSP通過VME總線采用HPI方式自動引導啟動,從上位機下載程序。上位機可以通過VME總線對板上數據進行實時監控。FPDP總線連接至處理機上的主DSP,包括FPDP/TM和FPDP/RM兩個功能模塊。我們只需要更改和重新下載FPGA程序,便可以完成DSP處理機上的FPDP/TM和RM端口配置,以便對應整個系統結構重組。此外,用于FPDP通訊的FIFO也用FPGA實現。

處理機工作流程如下:系統上電后,4片C6701通過VME總線從上位機獲取運行程序,并存入各自片內程序RAM,準備響應。前板將需要處理的數據流通過FPDP總線發送至本板FPDP/RM端口的FIFO中并且發送中斷,主DSP響應中斷后從FIFO中讀取數據并且完成分配,分別發送至三個從DSP的雙口RAM中。從DSP通過雙口RAM讀取數據并且進行并行處理,然后將處理完成的數據傳回雙口RAM。主DSP再將處理后的數據匯總并通過FPDP/TM端口發送至后板的FPDP/RM端口。如此循環,直至所有數據都處理完畢。最后主DSP將結果反饋至上位機,等待下次命令。

處理機中,每片DSP都配有一個256 K×8 bit FLASH芯片。處理機也可以脫離上位機單板工作,只需將程序提前下載到FLASH中。

3.2 單板電源設計方案

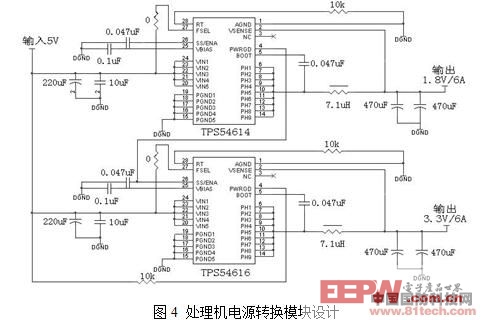

并行處理機板上需要的電源分為5V、3.3V和1.8V三類。其中5V直接來自VME機箱背板。3.3V和1.8V電源通過板上轉換模塊提供。由于本系統中DSP、CPLD和FPGA比較多,功耗也相對較高,其供電系統品質的好壞直接影響到整個處理機的工作穩定性。另外,并行處理機上的DSP和FPGA對其I/O電路和內核電路的供電順序也有一定的要求。

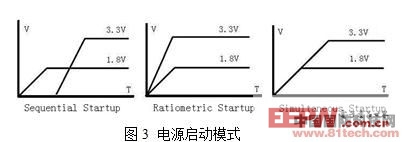

圖3給出了通用器件所要求的常見的3種電源啟動模式:Sequential Startup,即板上先提供1.8V電源然后再提供3.3V電源;Ratiometric Startup,即板上1.8V和3.3V電源同時以相同比率啟動并且同一時刻達到穩定值;Simultaneous Startup,即板上1.8V和3.3V電源同時啟動。我們在實際設計中一定要考慮到器件對供電系統的不同要求,這對處理機的穩定性具有極其重要的意義。

處理機上DSP和FPGA要求內核電路和I/O電路的供電采用Sequential Startup模式。整板需要5A左右的1.8V和3.3V 電源系統。由此,我們采用TI公司的TPS54614和TPS54616芯片設計了處理機的電源轉換模塊。它有體積小,輸出電流大,性能穩定等特點。電路原理如圖4所示。TPS54614采用5V輸入,能夠穩定提供最大電流為6A的1.8V輸出,TPS54616同樣采用采用5V輸入,能夠穩定提供最大電流為6A的3.3V輸出。此電源轉換模塊完全滿足整個信號處理機的供電量要求。

在設計中,根據TPS54610系列芯片的特性,我們將TPS54614的PWRGD連接至TPS54616的SS/ENA管腳。系統上電時,當TPS54614輸出電壓低于正常值的90%即1.6V時,PWRGD為低,抑制TPS54616啟動,當TPS54614輸出電壓大于1.6V時,PWRGD變高,啟動TPS54616;系統關閉時,TPS54614輸出降低到1.6V時,PWRGD變低,TPS54616才開始關閉。因此保證了DSP、FPGA內核電壓供電先于I/O電壓,滿足了系統供電采用Sequential Startup模式的要求。

評論