DSP的高速串行外設接口設計

3 SPI硬件設計

寄存器在SPI中起著決定性的作用.無論是在微控制器接口,還是SPI控制接口,寄存器在數據傳輸和控制方面都是主要的組成部分。而寄存器最基本最重要的單元是觸發器.只有改善觸發器的結構,才能提高整個SPI接口的性能。

有的串行接口設計中采用B結構的觸發器設計,這些結構里應用的是一種簡單的MOS管做開關.雖然MOS管做開關有功耗低,占面積小的優點。但要提高它的電路工作頻率.開關速度,制作丁藝卻是越來越困難。而且如果輸入信號不強.就很可能出現信號倒流,這就需要一個較高電壓來控制開關。這也不利于數據傳輸和降低功耗等等。

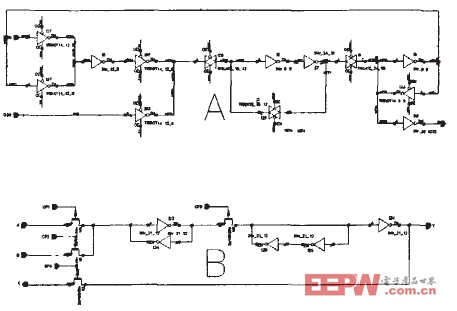

為了解決由MOS管做開關時引起的種種難題.來實現在TMS320LF2407串行接口中的信息傳遞的高速率。本設計綜合考慮速度、工作電壓、噪聲容限等因素的影響.采用了一種新穎的觸發器結構(圖4A部分),本文接口電路中大都采用了該觸發器的電路設計,工作電壓降低到3.3V,大大降低了整體功耗;在開關方面采用了三態門,有效的防止了信號倒流,實現了信號傳輸的穩定;添加了一個反饋信號,在需要的時候.能夠把所需反饋信號再次輸入;同時加快r開關速率,帶負載的能力也增強。

圖4 A、B兩種觸發器比較

4 RTL級設計

隨著數字系統設計的復雜性不斷增加,在設計初期指定有效的設計策略對于整個設計是至關重要的。行為描述方式是對系統數學模型的描述。它包括RTL、算法級、系統級的描述。RTL是指通過描述寄存器之間數據流動來描述數字電路系統,是一個數據流的概念.寄存器與寄存器之間的數據處理由組合邏輯完成。RTL級是Verilog較高抽象層次,在這個抽象層次上,模塊可以根據設計的算法來實現.而不用考慮具體的實現細節。

4.1寄存器整體電路設計

下面是部分Verilog HDL源代碼.描述了數據傳輸時相關寄存器的功能設置:先是對復位時各個寄存器的初始值,接下來是對寄存器進行功能設計.和數據傳輸時候產生的中斷使能和標志位的設計。

always @ (posedge Peri_clk or posedge RESET)

begin

if(RESET)

begin

outdb=8’hz; SPICCR=8’h00; SPICTL=8’h00; SPIBBR=8’h00; SPIPRI=8’h00;

end

end

always @(posedge Peri_clk or posedge RESET)

begin

if(RESET)

shift_out_d=1’b0;

else

case(1’b1)

spidat_w: SPIDAT=PeriDB; shifi_out_clk:shift_out_d=SPIDAT[7];

sample_in_clk:SPIDAT[7:0]={SPIDAT[6:0],sample in_d};

default;

endcase

end

always@(posedge Peri_clk or posedge RESET)

begin

if(RESET)

SPISTS=8’h00;

else

begin

if(SW_RESET)

SPISTS[7:6]=2’hO;

else if(int_flag_set)

begin

SPISTS[6]=1’b1;SPIBUF=SPIDAT;SPIEMU=SPIDAT;

end

else if(spibuf_r)

SPISTS[6]=1’b0;

if(overrun_flag set)

SPISTS[7]=1’b1;

else if(sts7_clr)

SPISTS[7]=1’b0;

end

end

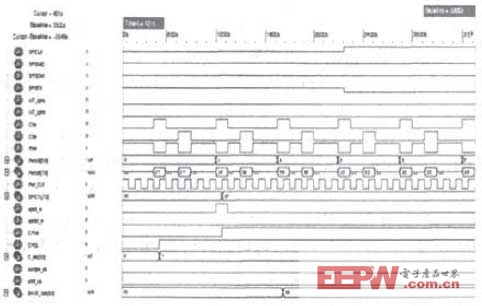

4.2整體時序仿真

將上述Verilog代碼編譯,再寫上對應測試代碼進行驗證。圖5是寄存器的寫操作的整體時序仿真波形圖.驗證了上述代碼正確可行。

圖5寫操作整體時序仿真

5 結論

本文作者的創新點是改進了硬件觸發器的結構.用三態門和傳輸門取代那種單一MOS管的結構。首次應用到TMS320LF2407芯片串行外設接口上,降低工作電壓到3.3V,加快數據傳輸,而且還有相應的反饋信號,進一步完善了觸發器結構。同時有很好的可移植性好。具有充分的可裁剪性,本設計運行可靠,達到預期的效果。

評論