基于DSP的高精度波形發生器系統設計

使用TMS320VC54X系列DSP控制模數轉換器AD7846,設計出幅度可精確至1毫伏的波形發生器。文中給出了具體的硬件實現框圖以及用來產生波形的DSP匯編源程序。

隨著電子技術的發展,波形發生器已經廣泛的應用在通信,控制,測量等各個領域。在很多地方,如測試測量領域,需要輸出的波形能夠精確地定位在某一整數值上,但通常由于ADC參考電平的限制,使之很難達到所需的精度,給系統的調試及軟件設計帶來諸多不便。本文采用了高精度的電壓參考芯片ADR434為模數變換器提供參考電平,使波形發生器的最低可調電壓達到125μV,為精確地輸出整數值電壓及其相應波形提供了方便的硬件環境。本設計具有輸出精確,控制靈活方便等特點。

系統設計

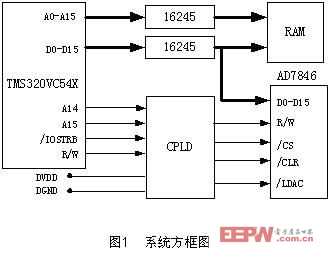

本系統采用TI公司生產的TMS320VC54X系列DSP作為核心控制器件,并采CYPRESS工司生產的CY7C1021V(64K*16RAM)來擴充DSP的外部數據存儲空間。在DSP與ADC及RAM之間的數據接口加入TI公司的74LVC16245(16位總線變換器)以增加DSP的驅動能力,并用來隔斷器件間的干擾。DSP與DAC之間的邏輯控制采用CPLD實現,這樣可以方便系統的設計與調試,本文中采用CPLD為ALETRA公司的EPM7064SLC84-10。整個系統的方框圖如圖1所示

器件簡介

本系統所采用的模數變換器為AD7846,它是美國AD(Analog Device)公司基于LC2MOS工藝生產的16位數模轉換器。它有和兩個參考電平輸入端以及一個片內放大器。標準情況下可以將其配置為單極性輸出(0V到+5V,0V到+10V)或雙極性輸出(,)。當然,改變和兩個參考電平輸入端的電平,也可以改變其輸出的動態范圍。如本文中便是采用高精度電壓參考芯片AD434提供參考電平,使DA的動態范圍設置為。

AD7846采用分段式結構。DAC鎖存器的高4位選通16個電阻串中的一段,段的兩端接有運放作為緩沖,運放的輸出反饋至12位的模數變換電路,并由該電路提供后12位分辨率。這種結構可以確保16位單調性,兩個緩沖運放間輸入失調電壓的高度匹配還確保了優良的積分非線性。

除了優良的精度指標外,AD7846與微處理器的連接也非常方便。它有16位數據I/O口以及四根控制線(,R/,以及)。R/與用來控制對I/O鎖存器的讀寫,信號用于多DAC系統中同步更新多片DAC數據,用于將DAC的輸出復位至0V。

AD7846參考電壓的設計

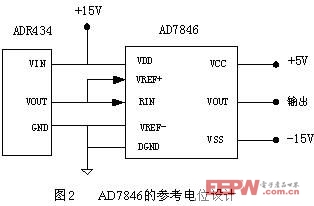

為了使系統的輸出波形在幅度上能夠精確到1毫伏,本文采用AD434為AD7846提供參考電壓。ADR434為AD公司生產的低噪聲,高精度,低溫漂的電壓參考芯片。它采用了AD公司的溫漂曲率修正專利技術,可以使其電壓對溫度的非線性達到最小。二者的具體連接如圖2所示。

圖2所示的連接方法使AD7846工作在雙極性輸出狀態下。AD434為DA提供+4.096V的參考電平,DA根據此電平經過雙極十六位線性分解,所得的最低可調電壓為4.096V/215=125μV。具體的編碼表如表1所示。

表1 AD7846編碼表

ADC鎖存器中的

二進制數

模擬輸出( )

最高位 最低位

1111 1111 1111 1111

1000 0000 0000 1000

1000 0000 0000 0001

1000 0000 0000 0000

0111 1111 1111 1111

0000 0000 0000 0000

+4.096V(32767/32768)=+4.095875V

+4.096V(8/32768) =+0.001V

+4.096V(1/32768) =+0.000125V

+4.096V(0/32768) =0V

-4.096V(1/32768) =-0.000125V

-4.096V(32768/32768)=-4.096V

邏輯控制及軟件實現

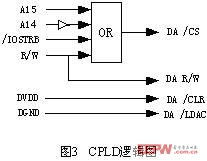

本文使用CPLD作為DSP控制DA的邏輯編程器件,將DA映射在DSP的I/O口,地址為4000H 7FFFH。AD7846一共有四根控制線,它們組成的控制邏輯如表2所示。

表2 AD7846控制邏輯真值表

/CS

R/W

/LDAC

/CLR

功能

1

0

0

X

X

X

X

0

1

X

0

1

X

X

X

0

X

X

X

X

X

1

0

0

使DAC的I/O鎖存器呈高阻態

數據(DB15DB0)裝入I/O鎖存器

I/O鎖存器中的數據輸出到數據線上

I/O鎖存器中的數據裝入DAC鎖存器

DAC鎖存器裝入數據000…000

DAC鎖存器裝入數據100…000

CPLD中燒入的邏輯圖如圖3所示。

對于波形的產生,通常有兩種方法。一種方法為使用算法計算輸出波形某點的幅度編碼值(如正弦波可通過泰勒級數展開得到),這種方法可直接精確地計算出每個角度的波形值,所占用的存儲空間小,但對于任意波形的輸出,所需的算法較為復雜,系統實時性也會受到影響。另一種方法為查表法,該方法可能需要占用較大的存儲空間,但軟件控制卻非常方便,實時性也更高。采用查表法的軟件控制可由如下代碼實現。

.mmregs

.global main

main:

nop

ori: stm #SINtable,ar2 ;將數據表頭地址送入ar2

ld #13H,a ;循環輸出20個樣點值

JUMP: portw *ar2+,4000h ;AD7846被配置在I/O口的4000H 7FFFFH處

rpt #1fffh ;改變rpt的值可以改變正弦波的頻率

nop

sub #1d,a

bc JUMP,aneq

b ori

SINtable ;正弦波幅度編碼表

.word 7FFFH .word 0A78DH .word 0CB3CH .word 0EF8DH .word 0F9BCH

.word 0FFFFH .word 0F9BCH .word 0E78DH .word 0CB3CH .word 0A78DH

.word 8000H .word 5872H .word 34C3H .word 1872H .word 0643H

.word 0000H .word 0643H .word 1872H .word 34C3H .word 5872H

.end

該段程序可使AD7846輸出標準正弦波,幅度范圍為4.096,頻率可通過改變rpt的值加以調節。若提供大量采樣點,可使其實時輸出高精度的任意波形。當然,利用DSP強大的運算處理能力,也可用軟件計算出所需波形的各點采樣值,這樣可以節省存儲空間,降低系統硬件成本。

結束語

本系統已經過實際測量,系統各部分工作正常,AD7846可精確穩定地輸出所需波形。該方案不僅達到了很高的精度與系統實時性,還具有控制靈活方便等特點,是一種很好的波形發生器。

評論