ARM存儲器之:存儲保護單元MPU

15.4.2內存訪問順序

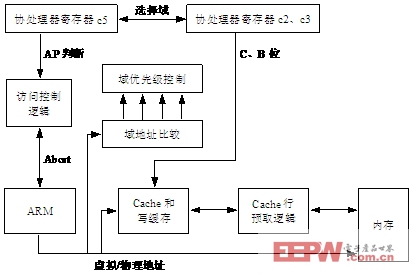

當ARM處理器產生一個內存訪問信號時,內存保護單位MPU將負責檢查要訪問的地址是否在被定義的域中。

①如果地址不在任何域中,存儲器產生異常。如果內核預取指令則MPU產生預取中止異常;如果是存儲器數據請求,則產生數據中止異常。

②如果地址在多個域內,由MPU判斷域的有效級來決定存儲區域的訪問屬性。訪問屬性可以在CP15的寄存器中設定,可設定的位為C(Cache)、B(Buffer)、AP(AccessPermission)。這些屬性的具體定義為:

·C和B可以控制Cache和寫緩存屬性的Cache策略。例如,可以設置一個域使用回寫(write-back)策略訪問存儲器,而另一個域則以無Cache和無寫緩存方式訪問;

·AP(accesspermission)決定域是否可以被訪問。如果在當前處理器模式下,該域不能被訪問,MPU將產生一個存儲器訪問異常。

圖15.16顯示了一個存儲器訪問過程。

圖15.16存儲器訪問過程

15.4.3使能MPU

通過對協處理器CP15的寄存器c1中的bit[0]置1,可以使能存儲器保護單元MPU。在系統上電時,默認狀態是該位清零,所有保護域無效。

在使能MPU之前,至少一個域要被設定,而且該域的屬性和訪問權限要預先設定好。

| 注意 | 在數據和指令域分離的系統中,如ARM940T,在指令和數據域中都要有一個有效域被預先設定好。 |

另外,使能MPU的指令要設在有效的域中。如果在使能MPU之前,域的屬性和訪問權限沒有設定,那么系統的運行結果將不可預知。

當MPU無效(將協處理器CP15寄存器r1的bit[0]置0)時,整個內存區域都被處理器視為無Cache、無寫緩存、無存儲保護狀態。

15.4.4重疊域

域的定義在MPU的作用下可以重疊。當重疊的域被訪問時,MPU會判斷域的優先權,決定使用那個域的屬性來操作重疊域。

域屬性優先級的排列順序為:域7的有效級最高,其次為域6,域0的優先級最低。

【例15.3】

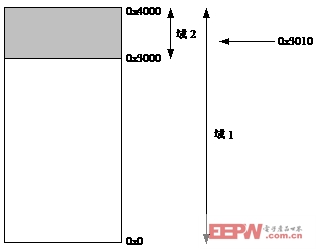

假設將一個從0x3000起始的4KB地址空間定義為域2,其訪問屬性AP定義為0b10(AP=0b10,特權模式讀/寫訪問,用戶模式只讀)。

將起始地址為0x0的16KB地址空間定義為域1,其訪問屬性AP定義為0b01(AP=0b01,特權模式只讀)。

系統域劃分如圖15.17所示。

圖15.17重疊域的訪問

當處理器在用戶模式下執行Load指令,從0x3010地址取數據時,0x3010地址既在域1中也在域2中,因為域2的屬性優先級高于域1,所有MPU執行域2的訪問屬性從0x3010地址取數據。域2是用戶模式可讀,所以不會發生數據異常。

在分配訪問權限時重疊區域比非重疊區域有更大的靈活性,它可以使內存的某個特定聯系內存單位在程序中擔任背景的作用,用來給一塊大存儲空間分配相同的屬性的低優先級域。其他具有較高優先級域的區域與該背景域某些部分重疊,用來改變已定義的背景域的較小子集的屬性。這樣,具有較高優先級的域可以改變背景域屬性的子集。背景域可以用來保護一些睡眠狀態的存儲空間,使其不受非法訪問,而此時由另一個不同域控制下的背景域的其他部分可以處于活躍狀態。

15.4.5與MPU相關的CP15寄存器

與MPU相關的協處理器寄存器主要是c2,c3,c5及c6。另外還有寄存器c1中的1到2位。

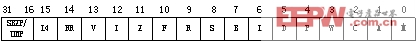

(1)c1中的MPU相關位

c1的編碼格式如圖15.18所示。

圖15.18協處理器寄存器c1編碼格式

M(bit[0])控制控制MPU的使能。

·M=0:禁止MPU

·M=1:使能MPU

A(bit[1])選擇是否支持內存訪問地址對齊檢查。

·B=0:禁止地址對齊檢查

·B=1:使能地址對齊檢查

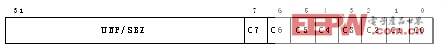

(2)c2中的MPU相關位

c2的編碼格式如圖15.19所示。

圖15.19協處理器寄存器c2編碼格式

寄存器位0~7分別對應域0~7的Cache屬性。位8~31應該設置成0。

| 注意 | 在數據和指令分離的系統中,通過MRC和MCR指令的第二個操作數opcode2>來決定讀寫D-Cache和I-Cache屬性。 |

存儲器相關文章:存儲器原理

評論