一種于FPGA的多通道頻率測量系統設計

3)對過濾后的真實被測頻率信號fre_real1進行上升沿判斷,以確定頻率計數的起始與結束,控制頻率計數器的計數與輸出過程。

本文引用地址:http://www.104case.com/article/256787.htm4)計數值輸出過程中,需設置count_delay來判斷頻率信號的周期是否大于1s,如果成立,則認定外部無頻率信號輸入,輸出值置為NAN(表示無窮大)。同時,系統啟動過程中頻率計數器已經開始工作,為了保證頻率計數的正確性,可設計cnt計數器,丟棄初次計數值。最后,將有效的計數值輸出給fre_data。

3 仿真驗證

使用ModelSim對可編程邏輯進行仿真。測量對象為1000 Hz方波信號,時鐘頻率為33 M,因此時鐘計數值應該是33 000。任選信號周期內的一個時刻作為系統復位點,仿真結果如圖3所示。從圖3可以看出,fre_data的值在第三個start信號凸起后變為33 000,與理論值完全一致,說明設計有效。

4 實測數據

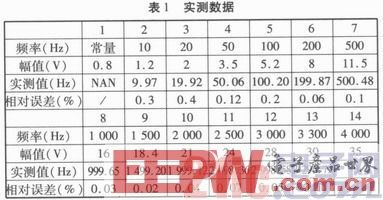

使用信號發生器提供不同頻率的正弦信號,對系統進行實測,所選取的頻率測試點覆蓋整個實際應用的頻率范圍,即20~3 300 Hz,且可以驗證可編程邏輯電路的數字濾波及延時判斷功能。同時,為了更好的模擬發動機實際情況,正弦信號的幅值應隨著其頻率的增大而增大。實測數據如表1所示。

從表1可以看出,當輸入信號的頻率小于1Hz時,系統的延時判斷功能生效,實測值為NAN(無窮大);當輸入信號的頻率大于3 300 Hz時,系統的數字濾波功能生效,實測值為0;當輸入信號的頻率介于1~3 300 Hz之間時,實測值的相對誤差不超過0.4%,與實際頻率基本一致。

5 結束語

文章提出了一種基于FPGA的多通道頻率測量系統的實現方法,主要創新點是利用可編程邏輯芯片搭建數字濾波電路,通過邏輯分析判別輸入信號是否切斷并做出響應,符合實際應用的需求。系統的擴展性強,電路結構相對簡單,仿真及實測結果表明濾波效果明顯,測量精度較高,在工程領域具備適用價值。

模擬信號相關文章:什么是模擬信號

fpga相關文章:fpga是什么

評論