基于ARM的多路同步A/D和D/A設計

2 多路同步D/A設計

本文引用地址:http://www.104case.com/article/255774.htm2.1 DAC8574的功能

DAC8574是帶有IIC接口的16位4路同步數模轉換芯片。DAC8574帶有一個IIC串行接口,包括SCL串行時鐘輸入和SDA串行數據輸入兩個引腳。輸出四路模擬電壓為VOUTA、VOUTB、VOUTC、VOUTD,電壓范圍為+2.7~+5.5V.由外部提供參考電壓VREFH、VREFL.A0、A1為IIC地址選擇,A2、A3為擴展地址選擇,A1、A0、A3、A2共可確定16個地址,在IIC總線上最多可擴展16個DAC8574.本設計在IIC總線上只使用一個DAC8574,則設置地址A1A0A3A2=0000.LDAC為同步輸出電壓更新。

DAC8574有三種工作模式:標準模式、快速模式、高速模式。標準模式時傳輸速率為100kbit/s,串行時鐘頻率fscl=100kHz,更新率為5.3kS/s;快速模式時傳輸速率為400kbit/s,fscl=400kHz,更新率為22.22kS/s;高速模式時傳輸速率為3.4Mbit/s,fscl=3.4MHz,更新率為188.88kS/s.標準模式和快速模式傳輸線協議基本相同,高速模式不同于標準和快速模式。DAC8574與S3C2440通過IIC總線連接時,DAC8574作為從機,S3C2440作為主機。本設計將DAC8574設置為高速模式。

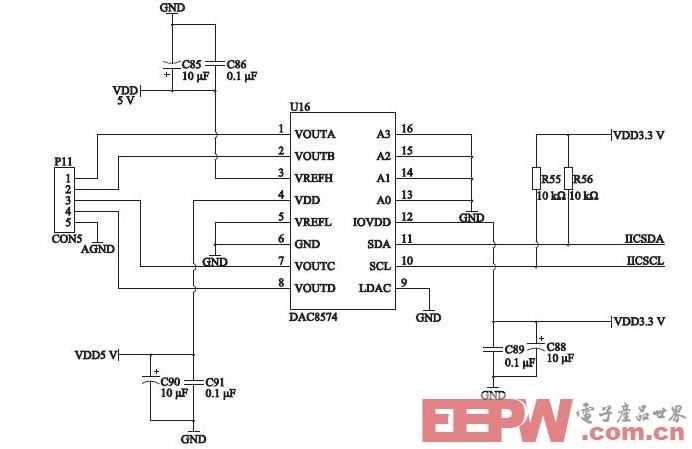

2.2 DAC8574與S3C2440接口電路設計

DAC8574通過IIC接口SDA、SCL引腳與S3C2440連接,其工作模式選擇、通道使能、LDAC功能是由S3C2440通過SDA輸入設定的。如圖3所示,電源電壓+5V,參考電壓+5V,IOVDD為+3.3V、LDAC接地。

?

圖3 DAC8574接口電路

2.3 DAC8574的接口程序設計

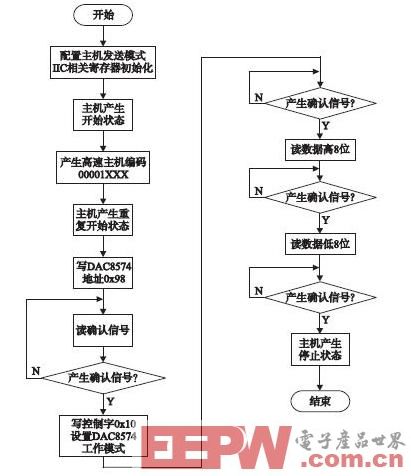

DAC8574作為從機,S3C2440作為主機,根據高速模式傳輸協議編寫DAC8574的接口程序。圖4所示為設計的DAC8574接口程序的流程圖。主機先產生一個開始狀態,隨后產生高速主機編碼的串行數據00001XXX.從機設備不需要確認高速主機編碼,但必須能夠識別并改變自身內部設置以支持3.4Mbit/s的高速傳輸。主機產生一個重復開始狀態,接著發送一個有效的從機地址字節,本設計的從機地址字節為10011000,包括7位DAC8574的地址1001100和1位讀寫控制位0(主機寫入從機)。地址匹配的從機識別地址后產生確認信號。本設計將控制字節設置為00010000,主機發送控制字節設置從機運行模式后,從機產生確認信號。隨后,主機發送數據最高有效位MSB,從機產生確認信號,主機再發送數據最低有效位LSB,從機產生確認信號并開始數據更新,這樣DAC8574就完成了一次數據接收與數模轉換。之后主機可以繼續向從機發送數據,最后主機產生停止狀態結束當前的數據傳輸。

圖4 DAC8574 工作程序流程圖

?

3 結語

該設計通過對程序的修改可改變其通道數、轉換速率、傳輸速率,因而具有一定的靈活性。而基于ARM處理器設計的系統還具有成本低、功耗低、實時性能好、智能程度高、可靠性高、體積小、易擴展、功能強、開發周期短等優點,在工業控制、信息技術領域有著廣闊的應用空間。

評論