利用芯片上時脈實現高性能全速測試

全速測試在大量新功能的協助下有了很大的改進,包括在測試模式期間使用芯片上產生的功能時脈。目前許多設計都工作在非常高的頻率,并包含許多時脈。芯片上鎖相環(PLL)是一種制作內部時脈的常見方法。通常伴隨PLL的還有乘法器、除法器以及其它時脈控制電路。不需要過多的附加邏輯,就能充分發揮用于測試的這些功能時脈的優勢。

大多數公司都會在設計進入布局階段之前使用靜態時序分析(STA)檢查功能時序。作為STA過程的一部份,設計師可規定設計時序約束和時序例外。本文所述STA過程的輸出是新思設計約束(SDC)文件,該文件包括了STA過程中其它工具需要的時序信息。

只要能正確地利用芯片上時脈,就能實現更高性能且更精密的的全速測試結果,但在實際過程中,必須注意到工具的選擇、不同特征尺寸元所具有的固有特性及其可能帶來的影響等,可能必須采取不同的相應措施來應對不同情況。由于目前芯片的幾何尺寸正不斷微縮小,缺陷與時序的關系將越來越密切,因此,在130nm以下的制程節點中,不應該完全依賴連續故障模型。本文將就以上觀點進行分析,并為設計師提供制作高品質全速測試程序的一些建議。

建議的方法

使用芯片上用于測試目的的功能時脈獲得比外部時脈更高精密度的結果。確保自動測試程序產生(ATPG)工具能夠利用芯片上時脈和時脈邏輯實現全速測試圖案。

如果組件的制造特征尺寸在130nm以下,應在測試儀器中增加轉換故障模型測試圖案。該模型可透過查找每個內部節點上的緩慢上升或緩慢下降變化檢查出時序缺陷。

在測試關鍵路徑或整體組件時序表征檢查時使用路徑延遲故障模型。一些公司也使用路徑延遲故障模型進行速度分級。

使用靜態時序分析定義和規定時脈與時序的關系,使設立和保持時間能被檢查。路徑的寬松時間也可以計算,有助于發現最關鍵的路徑。這些路徑再送到ATPG工具制作路徑延遲圖案。此外,時序例外路徑也有規定。

使用能夠在圖案產生期間自動處理時序例外的ATPG工具。

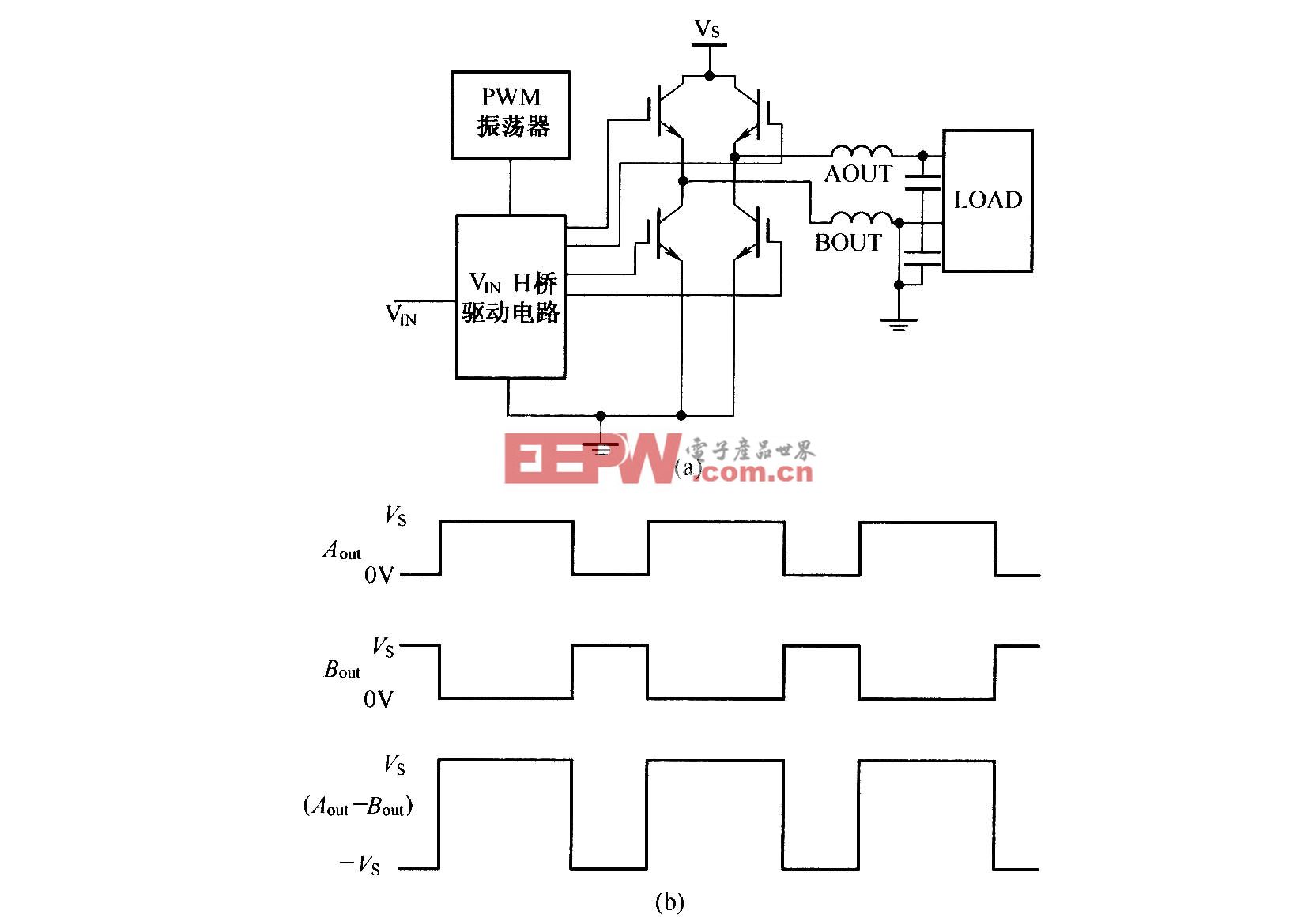

圖:采用傳統方法來處理時序例外路徑的五個設計范例,與在SDC檔案中進行讀取,且僅需增加X軸的新方法比較。

不建議的方法

如果組件上已經有這些功能時脈,就不應該為了支持高速時脈而在復雜的自動測試設備上花費太多的時間。一些接腳的I/O焊盤無論如何都無法處理很快的外部時脈速度。

采用130nm以下制程制造的設計不應該依賴連續故障模型。許多相關論文指出,隨著幾何尺寸的縮小,缺陷與時序的關系將越來越密切。許多問題與在組件上制作小于制造用微影波長的特征尺寸和外形有關。

不解決故障和多周期路徑就制作全速測試圖案。如果這些問題不解決,ATPG工具制作的測試圖案期望值將是組件無法實現的,極易導致測試圖案的仿真失配,并可能使好的組件無法通過測試。

在ATPG過程中只約束X軸的時序例外路徑端點。這種傳統方法將降低測試覆蓋率,并導致測試圖案儀上有更多的X點。它會屏蔽掉適用于其它全速測試路徑的觀察點,使芯片的某些部份無法被測試到。

評論