基于FPGA的2M誤碼測試儀系統的設計方案

2.2 E1接口電路的設計

E1的標準傳輸線路碼通常采用三階高密度雙極性碼(HDB3,high density bipolar),它是一種雙極性歸零碼,是廣泛用于PCM線路的傳輸碼型。本文中的E1接口選用非平衡的75 Ω物理接口(一收一發)。E1接口芯片ET2154是一路E1PCM-30/ISDN-PRI收發器,它集成有時鐘數據恢復及發送E1脈沖成型的片內線路接口單元(LIU)和E1幀處理器(Framer),其各項指標符合ITU-T的G.703、G.704、G.706、G.823建議等要求。 ET2154的線路接口功能主要包括三部分。第一是接收器,用于處理時鐘和數據恢復;第二是發送器,用于形成波形和驅動E1線路;第三是抖動抑制器。

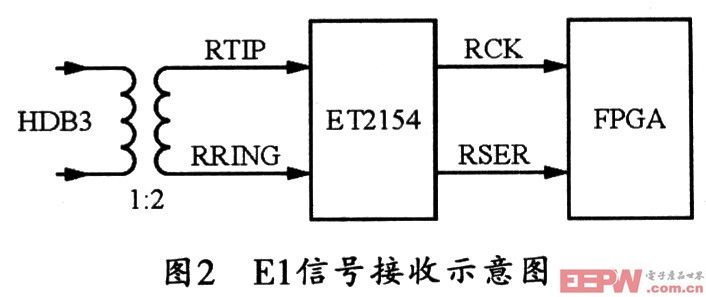

(1)E1線路接收接口

當HDB3碼流從E1線纜經BNC接口進入,并通過一個1:2的變壓器耦合至RTIP租RRNG輸入管腳后,其接收模塊將允許用戶設置寄存器以匹配外部線路的阻抗。ET2154中的數據時鐘恢復模塊可從HDB3碼流中恢復時鐘和數據。從HDB3碼流中恢復出時鐘和數據可通過高倍采樣來實現,首先由外部提供一個2.048 MHz的時鐘信號,然后由芯片內部PLL將它16倍頻到32.768 MHz 。即先對每位HDB3碼進行16倍的采樣,然后由時鐘恢復系統利用16倍的采樣時鐘來恢復時鐘和數據。其E1信號接收示意圖如圖2所示。

正常情況下(RTIP,RRING有信號輸入),在RCK(接收方向恢復時鐘)管腳輸出恢復后的時鐘信號。而當ET2154被配置成輸出NRZ數據模式時,則在RSER管腳輸出恢復出的串行數據信號并送入FPGA。

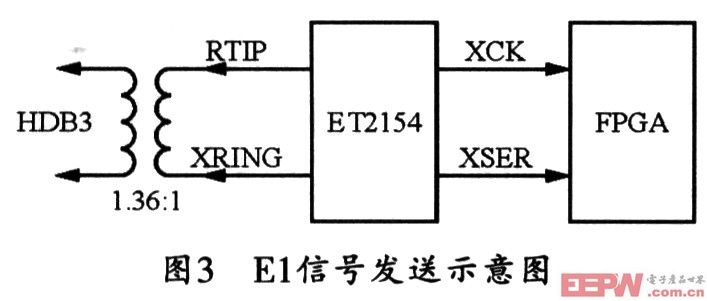

(2)E1線路發送接口

待傳輸的串行數據流一般由XSER (發送串行數據NRZ)管腳進入ET2154,并在XCK(發送方向輸入時鐘)管腳接收來自FPGA的2.048 MHz的時鐘信號。ET2154主要由內部精密的數模

(3) E1線路控制接口

ET2154的工作方式和特性是通過對其外部管腳的控制來實現的。通常將這些控制管腳連接至FPGA的外部I/O口,由FPGA來進行控制。ET2154 與FPGA的連接電路如圖4所示。ET2154通過內部寄存器的配置來設置其工作方式,FPGA則利用8位數據/地址復用線AD0~AD7來對 ET2154內部的寄存器進行設置,從而實現所需要的功能。

評論