串行數據測試中的CDR

在收發器接收端除了采用如圖1所示的PLL來恢復時鐘外,另一種時鐘恢復方法是使用相位內插器(phase interpolator,簡稱PI),在FBDIMM和PCI Express中都使用PI來恢復時鐘,但是使用儀器測試時,可以用PLL來建模。

測試高速串行數據信號的眼圖與抖動的儀器都使用了基于鎖相環的時鐘恢復方法。其中,實時示波器主要使用軟件PLL來恢復參考時鐘,取樣示波器和誤碼率測試儀都使用硬件PLL來恢復時鐘。實時示波器作為最普及和廣泛應用的測試儀器,本文僅介紹實時示波器的軟件CDR和眼圖測試、抖動測試的關系。

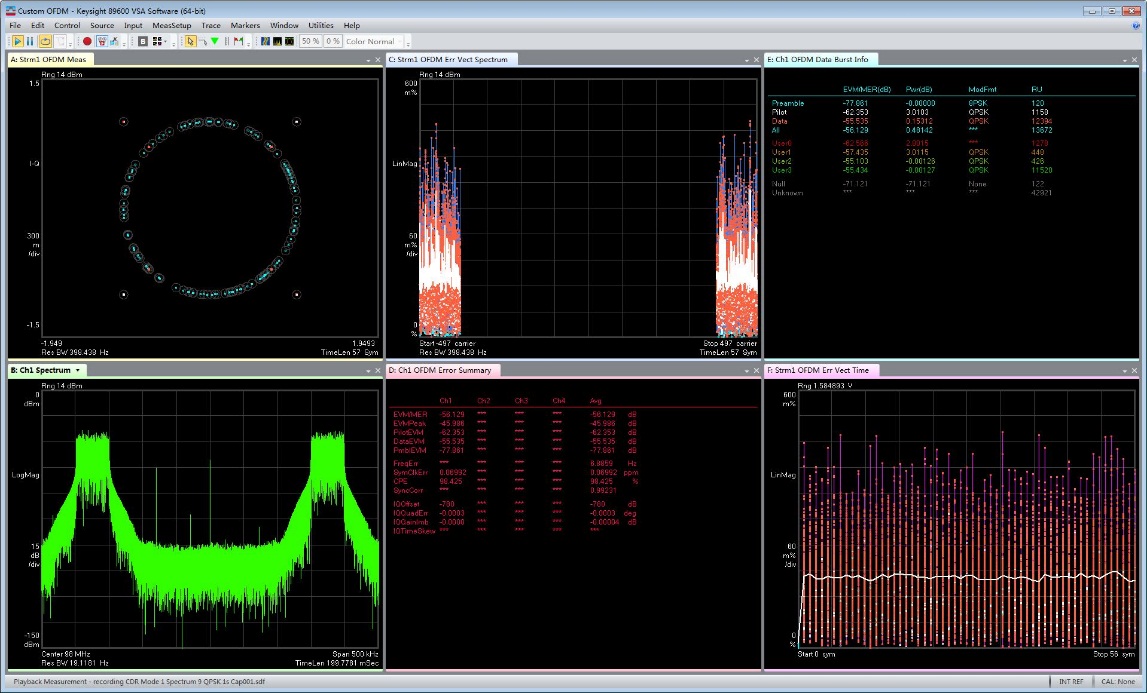

如下圖4所示為力科串行數據分析儀中PLL設置的參考,缺省情況下使用FC Golden PLL,該PLL為1階鎖相環,其環路帶寬等于比特率除以1667,最早是在Fibre Channel的MJSQ文檔中定義的。

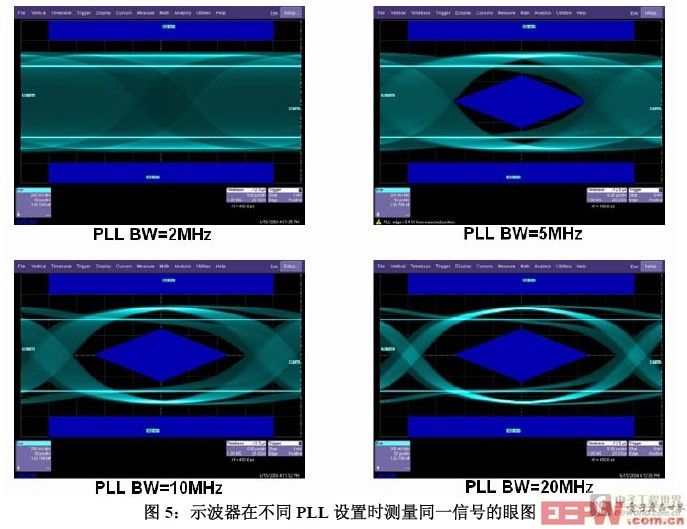

如下圖5為使用力科示波器測量某2.5Gbps信號,當示波器的串行數據分析軟件的PLL帶寬在2MHz、5MHz、10MHz、20MHz四種設置下的眼圖測量結果,可見,PLL帶寬越高,眼圖越清晰,抖動越小。問題是,待測試電路的收發器RX端接收到的、真實的眼圖和抖動是什么樣呢?答案是必須把示波器的CDR參數設置得和待測試電路RX端的CDR參數完全一致,這樣示波器的測量結果才具備參考價值。

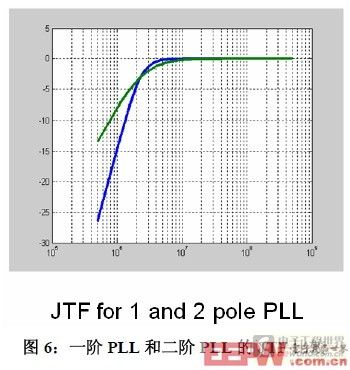

在圖4和圖5中都是一階鎖相環的CDR,在很多的串行電路標準中都使用這類PLL,比如GBE、XAUI、SDH、CPRI、FC、SAS等等。不過,PCIe Gen2、SATA2、Displayport則使用了二階鎖相環的CDR,如圖6所示為一階PLL和二階PLL的JTF對比,二階PLL有更加陡峭的滾降系數-40dB/decade(一階PLL的滾降系數為20dB/decade)。假設某500kHz的抖動為150ps(而且500kHz在斜線的頻段內),通過一階PLL后抖動只有15ps,而通過二階PLL后僅為1.5ps。可見,對于圖6中低頻段的抖動,二階PLL可以更大幅度的降低該頻段的抖動。

圖7所示為某2.5Gbps信號,CDR使用一階PLL或二階PLL的眼圖測量結果,可見,使用二階PLL得到的眼圖非常清晰、抖動更小。二階PLL可以更大程度的減小低頻抖動,通常用于帶有擴頻時鐘(SSC)的串行數據信號,比如計算機主板上的SATA和PCIe。

評論