實現射頻信號源的低相位噪聲及高速頻率切換的共存

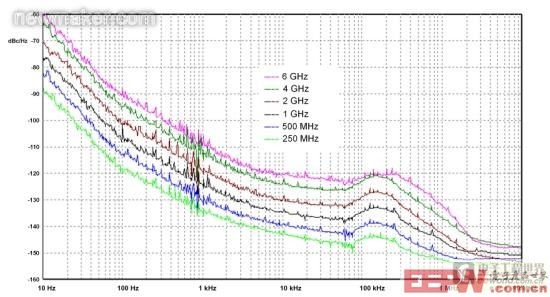

圖 3: Aeroflex S-Series SGA 模擬信號發生器典型相位噪聲特性圖示

輸出環路將兩個低噪聲信號相加。本底低噪聲壓控振蕩器 (VCO) 額定頻率范圍500 MHz至 667 MHz 增加一倍,達到 1000 MHz 至 1333 MHz。這個信號與低噪聲高頻信號混合。然后,利用差頻對內插信號進行相位比較。鑒相器輸出經低通濾波后,通過反饋控制 VCO 構成完整的 PLL。

倍頻程頻率合成器一般采用 VCO 庫覆蓋輸出范圍,因為低噪聲倍頻程調諧范圍不是直接完成的。為實現所需調諧范圍,可將 1/3倍頻程 VCO 放大3、4或5倍覆蓋一個倍頻程。

這種乘法器采用噪聲低于以前設計的方法。1000MHz 至 1333MHz 信號可再放大一倍,達到 VCO 頻率的4倍。這個信號可用來直接生成4倍輸出,或與本底 VCO 信號混合生成3倍和5倍 VCO 頻率。可調帶通濾波器選擇上、下邊帶。這種采用倍增器加混頻器的方法可保證整個倍增頻率范圍內的噪底低于采用其他方法。

快速頻率切換的實現及其設計

實現 100 μs 內完成頻率轉換,同時保持低噪聲進一步提出了許多挑戰。頻率合成器至預調 VCO 和頻率可調變容二極管帶通濾波器存在多處模擬電壓。足以靈活地在幾微秒內完成電壓調諧,且保持噪聲低于幾毫微伏,切換后無飄移是相互矛盾的要求。我們的方法是嚴格篩選并選擇低噪聲 DAC、帶寬可變無源濾波器和介電吸收系數低的濾波器電容。

小數乘法器和輸出加法環路中的 PLL 采用基于混頻器的鑒相器。雖然本底噪聲很低,但它們的缺點是捕獲范圍有限,這是保證 PLL 環路帶寬的必要條件。搜索振蕩器等傳統鎖相方法對于這種應用來說速度太慢。當粗調預設相位將 VCO 頻率調整到正確范圍后,可在鎖相之前采用數字鑒相技術 (已申報專利) 精確調整 VCO。FPGA 比較鑒相器兩個信號的頻率,通過修改預設電壓將 VCO 調整到正確頻率。

由于PLL最小帶寬為200 kHz,當VCO極為接近鎖定時,可以非常迅速鎖定設定頻率,頻率設定可達到 100 μs 的 0.1 ppm。1-GHz 載波頻率的誤差范圍僅為 100 Hz。

頻率調制

頻率合成器采用標準兩點調制生成寬頻帶、寬頻偏調制。FM 系統可利用先進的低成本數字處理技術設置整個 FM 增益,匹配兩個內部校準通道的增益和延遲。調制信號可同時加給輸出 VCO 和內插頻率合成器。由于同時變化,輸出 PLL 在鑒相器處無誤差。AC 和 DC 輸入耦合,以及相位調制也可以采用數字化方式處理。

結束語

頻率合成器利用模擬和數字組合技術實現設計目標,使 Aeroflex S-Series信號發生器具有優異的性能,充分體現了Aeroflex產品線幾十年來不斷推動信號發生器技術進步的顯著特點。

評論