寬帶阻抗測量儀的設計——微處理器電路設計(二)

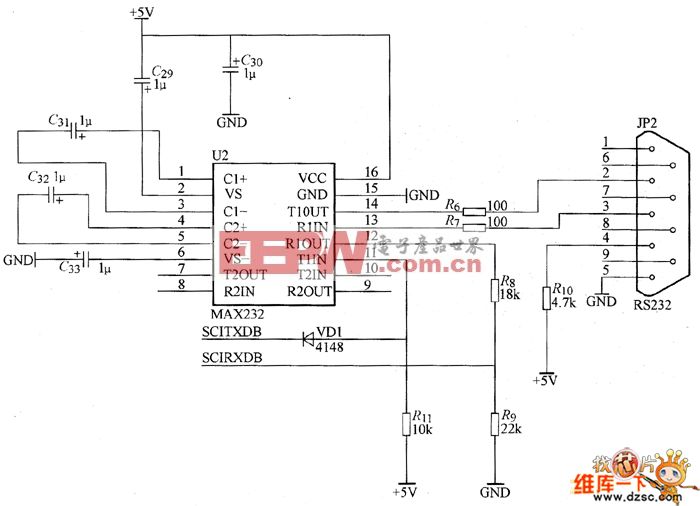

RS232選用了Sipex公司的SP202EEN,RS232串行總線收發器,該芯片具有低功耗,高傳輸率的特點,工作在5V工作電壓下,滿足所有的符合RS232D和ITUV.28標準。電路原理圖如圖5-7所示。

RS485接口選用了TI公司的SN65HVD485E總線收發器[33-35],該芯片也是+5V供電,完全兼TIA/EIARS485A標準,適用于長雙絞線最高10Mbps的數據傳輸,靜電防護等級15KV。電路原理圖如圖5-8所示。

5.3.2 USB接口電路

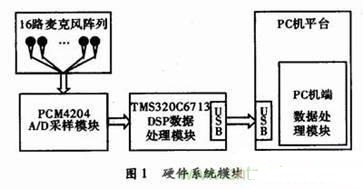

設計USB總線具有傳輸速度高、熱插拔、即插即用等特點,目前被廣泛的使用,本設計為了方便系統與外部設備的通訊也設計了USB接口。

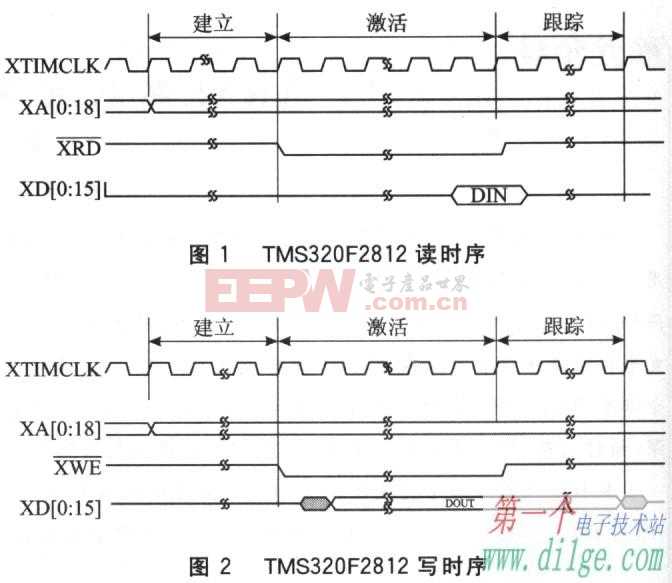

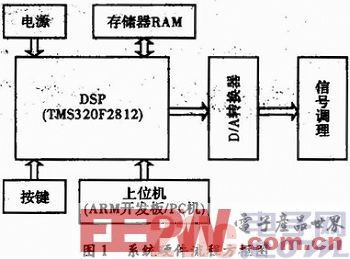

系統采用Cypress公司的CY7C68001芯片實現USB2.0接口。CY7C68001通用USB2.0接口控制器是基于應用層編程的接口器件,相對于其它基于鏈路層編程的接口器件,使用簡單,開發方便。CY7C68001上集成了USB2.0收發器(物理層)、USB2.0串行接口引擎SIE(鏈路層,實現底層通信協議)。CY7C68001作為F2812的外設,USB的應用層協議由F2812編程實現。CY7C68001采用并行異步存儲器接口與F2812相連接,主機可以喚醒F2812,亦可以配置USB。

CY7C68001符合USB2.0規范;支持高速(480Mbps)或全速(12Mbps)USB數據傳輸;4個可編程端點共享4KB的FIFO,每個端點對應的FIFO空間大小及FIFO狀態可編程;8/16位雙向命令接口、配置靈活(同步/異步可配置,狀態引腳、讀寫引腳以及極性可編程),數據I/O口可與DSP、FPGA或其它ASIC同步/異步通信;智能SIE功能(可在不借助微處理器中斷的前提下完成枚舉);集成的鎖相環功能;I/O口為3.3VTTL電平,可承受5V電壓。

TMS320F2812與CY7C68001的接口電路如圖5-9所示。

CY7C68001相關引腳說明如下:FD[01:016]偽數據總線,FA[0:2]地址線和CS片選信號合起來為CY7C68001的地址空間。CY7C68001除了存儲器接口外,還有1個中斷信號USBINT和4個狀態信號(READY,FLAGA,FLAGB和FLAGC).USBINT信號表明CY7C68001有中斷事件發生,或反映對于CY7C68001的讀操作結束;FLAGA、FLAGB、FLAGC報告由FIFOADR[2:0]選擇的FIFO狀態,默認分別對應為FIFO自定義、滿、空狀態;FLAGD為FIFO狀淘片選可選,默認為片選信號;SLOE是CY7C68001驅動并行數據總線,常與SLRD短接;SLRD為并口讀有效信號,在SLRD有效且同步通信時,FIFO指針在每個IFCLK的上升沿遞增;SLWR為并口寫有效信號,在SLRD有效且同步通信時,FIFO指針在每個IFCLK的上升沿遞增;PKTEND信號總是高電平,將當前的緩沖區提交給上位機USB。

p2p機相關文章:p2p原理

評論