FPGA及動態可重構技術在軟件無線電中的應用

摘 要: 介紹了將現場可編程門陣列(FPGA)專用硬件處理器集成到軟件通信體系結構">軟件通信體系結構(SCA)中的機制,實現了動態部分可重構技術在軟件無線電(SDR)硬件平臺中的應用,有效地縮短系統開發周期,提高了硬件資源的利用率。

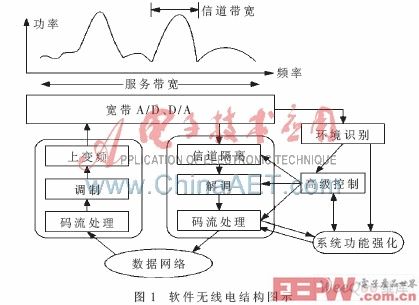

SDR是使用一個簡單的終端設備通過軟件重配置來支持不同種類的無線系統和服務(包括2G、3G移動通信系統和WLAN)的新技術。它具有較強的開放性和靈活性,硬件采用標準化、模塊化結構,可以隨著器件和技術的發展而更新和擴展;軟件模塊可以進行加載和更改,根據需要不斷升級。軟件無線電的結構如圖1所示,主要分為實時信道數據處理部分、環境管理部分、系統分析和功能強化部分。實時信道數據處理部分包括A/D、D/A、變頻、信道分離、調制解調以及碼流處理等數據模塊。

SDR的核心是聯合戰術無線電系統JTRS(Joint Tactical Radio System)的SCA規范,它對模塊化可編程無線通信系統的硬件體系結構、軟件體系結構和安全體系結構以及應用程序接口(API)規范進行了描述,同時引入了嵌入式微處理器系統、總線、操作系統、公共對象請求代理體系(CORBA)、面向對象的軟件和硬件設計等一系列計算機技術,并采用了“波形應用”和“資源”可裁剪、可擴充的設計思想,從而保證了軟件和硬件的可移植性和可配置性。

以接收機為例,SDR中A/D模塊之后的部分通過軟件來實現。本文在FPGA平臺上實現信號的調制解調,以滿足高速數字信號處理發展的需求。在Xilinx Virtex2Pro FPGA硬件平臺上實現了美國軍方短波通信系統標準MIL-STD-188-110B調制解調器,其中引入了動態部分可重構技術,提高了配置速度和硬件資源的利用率。

滿足SCA規范的波形組件之間通過CORBA總線通信,而FPGA平臺的專用處理器要實現對CORBA的支持比較困難。本文利用SCA規范中的SHP組件兼容性補充協議CP289提出了這一問題的具體解決方案。

1 FPGA的動態部分可重構技術

FPGA的動態可重構技術是指對時序變化的數字邏輯系統,其時序邏輯的發生不是通過調用芯片內不同區域不同邏輯資源的組合實現,而是通過對具有專門緩存邏輯資源的FPGA進行局部或全局芯片邏輯的動態重構而實現。部分重構是指重構器件或系統的一部分,在此過程中,其余部分的工作狀態不受影響。

FPGA部分可重構有多種實現方法,較為常用的是基于模塊化設計方法和EAPR(Early Access Partial Reconfiguration)設計流程,后者較前者而言,是一種較新的設計方法,并且有相應的軟件可以代替命令行方式進行實現,本文采取的就是這種實現方法。

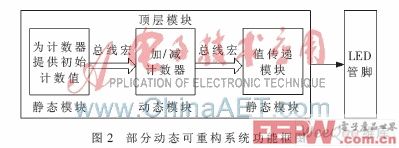

圖2所示為一個簡單的基于EAPR設計流程生成的部分動態可重配置系統。整個系統劃分出靜態模塊和動態模塊,之間的通信通過總線宏來進行。該系統通過FPGA板子上的dip開關為輸入引腳提供輸入數據,確定計數器的初始值。通過下載不同部分的比特流可以實現加、減計數功能的動態切換。計數結果通過值傳遞模塊接到FPGA板子上的LED管腳。整個設計過程可以概括為:

(1)模塊劃分:靜態模塊和動態模塊;

(2)頂層模塊與靜態和動態子模塊的設計及綜合;

(3)編寫初始用戶約束文件,主要指定I/O管腳約束和時鐘約束;

(4)在PlanAhead中進行EAPR設計:

①建立局部可重構工程;

②為每一個PRM定義可重配置實體;

③為PRM規定可重配置區域;

④放置總線宏和全局時鐘邏輯;

⑤運行DRC檢查;

⑥分別實現靜態邏輯和PR模塊;

⑦裝配并生成全局和部分比特流。

2 基于FPGA的SDR硬件體系結構及DPR實現

Xilinx Virtex2Pro FPGA內含處理器,通過一定的軟件編程,可根據環境及外部需求采用不同的調制解調算法處理通信系統中的數據。通過DPR技術,可以實時快速地調整算法中的參數或者實現不同算法之間的切換。

2.1 基于FPGA的SDR硬件平臺

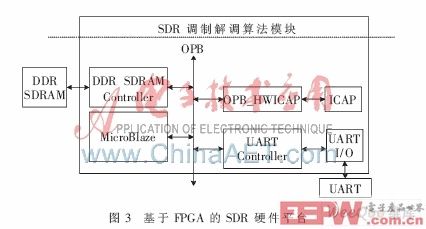

本文基于Xilinx Virtex2Pro FPGA,搭建的SDR硬件平臺如圖3所示。該系統以軟核處理器 MicroBlaze為核心,DDR SDRAM Controller、OPB_HWICAP和UART Controller通過OPB總線與處理器通信。DDR SDRAM為片外處理器,UART為串口設備,ICAP為內部訪問互連接口,主要用于部分重構。

評論