FPGA在頻率綜合器中的應用設計與電路

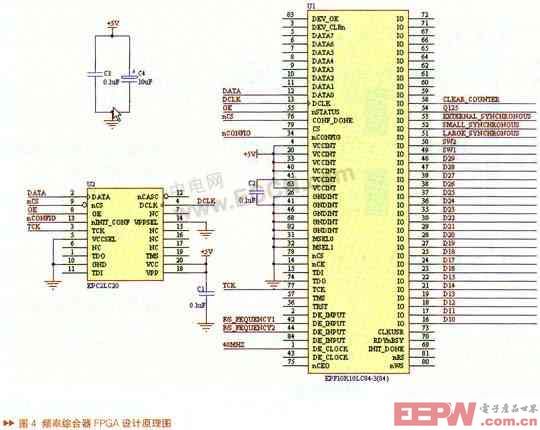

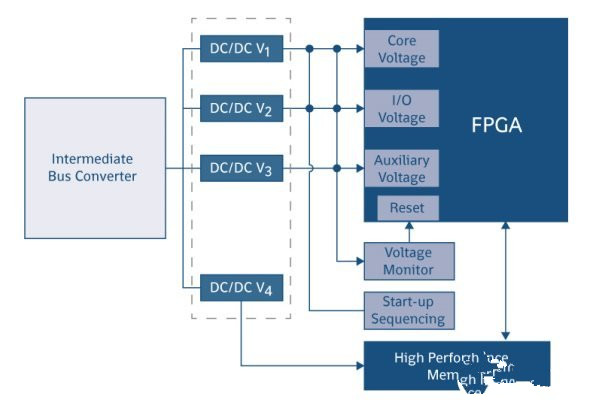

因為EPF10K10是RAM型器件,設計程序需固化在外部串行自舉器件EPC2里,在上電時,PF10K10把設計程序從EPC2讀入RAM并運行。頻率綜合器的FPGA設計原理圖見圖4。

頻率綜合器輸出信號

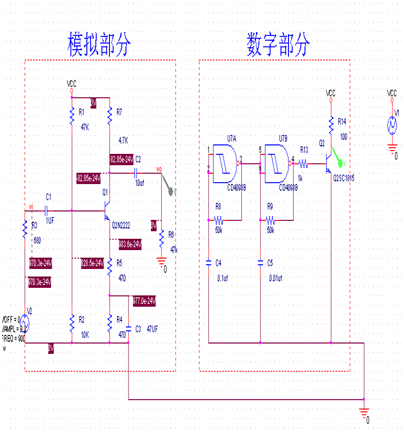

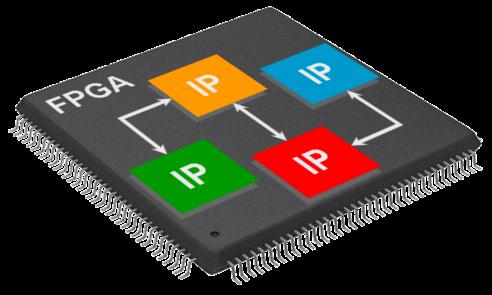

頻率綜合器的核心FPGA控制著鎖相環1、鎖相環2和開關調制器,使頻率綜合器工作在不同的狀態。

跳頻模式

工作在跳頻模式時,頻率綜合器輸出信號有跳頻同步、外同步、小同步以及大同步。

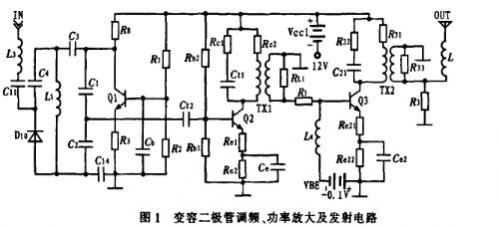

射頻信號:

1路輸出:1000-1504MHz,每步跳8MHz,一個周期共64步,后接開關,脈寬120nS,開斷>85dB,上升沿5nS,插損2.8dB;2路輸出:900-1404MHz,每步跳8MHz,一個周期共64步。點頻模式1、2工作在點頻模式時,頻率綜合器輸出信號有外同步、小同步和大同步。工作在點頻模式時,頻率綜合器鎖定在一個頻率點上,點頻模式1和點頻模式2工作方式相同,只是脈沖重復周期不同。點頻模式時,跳頻同步不存在,但是外同步可調仍然需要,小同步脈寬變為500nS,脈沖重復頻率為50kHz。

同步控制信號

大同步信號:周期為3.15mS的矩形脈沖,前后沿抖動8nS。

跳頻同步信號:脈寬120nS,周期為25μS,前后沿抖動8nS。

小同步信號:脈寬120nS,周期為25μS相對于跳頻同步脈沖延時10μS,前后沿抖動8nS。

外同步信號:與小同步信號相同,并且延時可調,作為脈沖放大器的時鐘同步信號。

波形文件

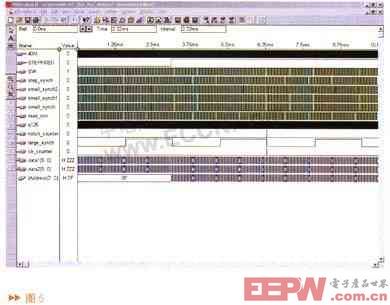

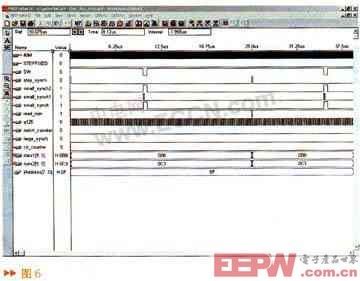

在MAX+PLUS II軟件開發平臺上加以40MHz的激勵信號,便可以驗證設計正確與否,主要是通過波形文件來驗證。波形文件見圖5、圖6。

結論

把FPGA技術運用在頻率綜合器中,使用器件少,邏輯功能可重復編程,滿足用戶后續改變功能的要求,它不改變原來的硬件設計,只需通過修改軟件就可實現。

評論