一種基于FPGA的實時視頻圖像處理算法

本文引用地址:http://www.104case.com/article/249273.htm

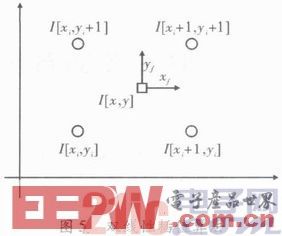

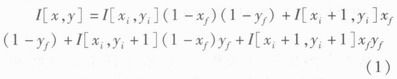

視頻插值模塊實現對視頻按比例因子進行雙線性插值放大處理。雙線性插值算法的基本原理如圖5所示,圖中的下標i和f表示各自坐標的整數和小數部分。雙線性插值是采用可分離的線性插值將4個最近的像素值組合,如式(1)。

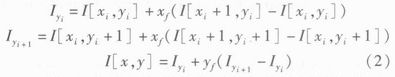

線性插值的結果與插值的順序無關。先進行y方向的插值,然后進行x方向的插值,所得結果相同。將式(1)進行分解,則有

當輸入分辨率有所變化而引起縮放因子變化時,FPGA內的數字邏輯能實時計算出式(2)中的系數xf和yf。而非僅計算幾種固定縮放比例,從而提高了算法模塊的利用率。

若以將攝像機1 024×576分辨率的圖轉化為1 366×768的圖為例,則水平縮放因子sc_x和垂直縮放因子sc_y均為0.75。若將水平因子直接帶入編寫程序,則會報錯。采用浮點數表示法,轉換后得到的10位16進制數,計算出系數xf和yf均為h300。

在實際設計中,為避免運算過于復雜,把復雜的運算分成幾個步驟,分別在不同的時鐘周期完成。插值計算的邏輯結構模塊如圖6所示。

系統包含3種不同的時鐘頻率:原像素點頻率clkin、輸出像素點頻率clkout和系統主時鐘頻率clksys。令系統主時鐘頻率為4倍的原像素點頻率,則使用Verilog語言及ModelSim SE 10。1 a和Quartus II仿真環境進行編譯,得到雙線性插值計算模塊的仿真波形如圖7所示。為程序書寫方便,將采集的4個像素值標為a、b、c、d,經過插值模塊后的輸出像素值為p。從仿真波形可看出,完成了雙線性插值計算模塊的實現。

3 結束語

針對大屏幕特點,從拼接控制器入手,提出了一種基于FPGA實現的視頻實時處理系統。主要采用雙線性插值法,討論了如何用FPGA實現,并進行邏輯結構的優化,提高系統性能,并對雙線性進行仿真,驗證了算法在拼接顯示系統中的可行性。圍繞拼接控制器這個應用方向,還有更多的問題需要進行研究,例如畫面自由疊加與漫游,單屏分割,自動圖像識別重建等。

fpga相關文章:fpga是什么

負離子發生器相關文章:負離子發生器原理 塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論