一種基于軟件關機電路的電源系統設計方案

本文引用地址:http://www.104case.com/article/249218.htm

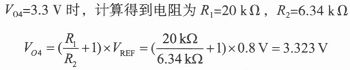

在設計過程中,如圖5,圖6所示,考慮到DSP內核的上電時間應比I/O模塊的上電時間提前或同時發生,而兩模塊供電又是分開的,因此需設計硬件延遲電路。

(其中,VTH=1.2 V、IENX=6μA、R=51 kΩ),這里取C=12 pF時,延遲時間為tDELAY=100 ns。

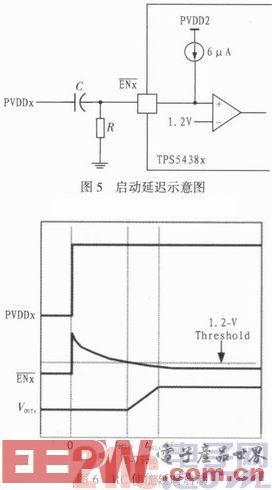

3.1 CVDD和CVDDSP的隔離

ARM內核和DSP內核上電順序如圖7所示,DSP內核的上電時間晚于ARM內核的上電時問,ARM上電后,使整個系統開始正常運轉,而進行數據處理的DSP內核應在ARM上電一段時間后上電或不上電。所以對其提供1.3 V電壓時,兩內核之間需使用功率電感延遲電流,起到隔離的作用。設計時,將CVDD直接連接1.3 V電源,而CVDDSP經過一個功率電感后,再連接1.3 V電源。

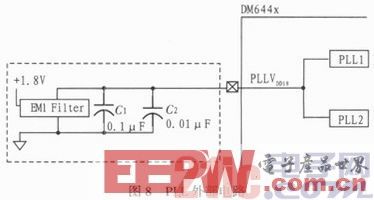

3.2 PLL電源設計

開關電源干擾主要來源于工頻電流的整流波形和開關操作波形,這些波形的電流泄露到輸入部位就成為傳導噪聲和輻射噪聲,泄露到輸出部位就形成了紋波問題。PLL外部電路如圖8所示,考慮到電磁兼容性的有關要求,在外部設計時加入EMI濾波網絡,隔離外部電源紋波引入,抑制開關電源上的干擾。

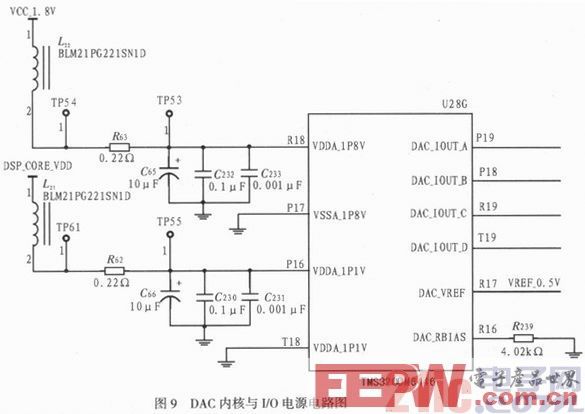

3.3 DAC內核電壓和模擬I/O電壓的設計

由于DSP內核電壓(Vcore=1.3 V)不能直接供給DAC內核(VDDAIPIV=1.2 V),為增強DAC內核電源穩定性,如圖9所示,采用功率電感L21,L22進行紋波濾波處理。而DAC的參考電壓0.5 V無需吸入大電流,因此直接選用穩壓二極管就能實現。模擬I/O電壓VDDAIP8V=1.8 V,設計方法與上相同。

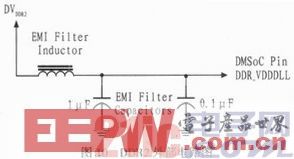

3.4 DDR2電源設計

DDR2外部電路圖如圖10所示,DVDDR2通過EMI濾波網絡將1.8 V電壓接入到DDR_VDDDLL引腳,實現對DDR2供電的目的;由于DDR2接口端輸入阻抗大,所以DDR_VREF參考電壓通過兩個阻值為1 kΩ的電阻分壓為0.9 V。

4 結論

嵌入式虹膜識別系統的電源網絡采用軟件關機電路進行控制,滿足了810 MHz的DSP等各類高功耗內核的需求,并解決了內核上電時序先后順序及其延時問題,提高了系統的穩定性和可靠性。該嵌入式虹膜識別系統現已量化投產,并成功投入社會使用。根據其實際應用表明,該電源系統具有可控性好、電壓穩定、寬輸入電壓,并滿足嵌入式系統所有器件功耗需求等的特點,達到了設計要求。

電路相關文章:電路分析基礎

評論