基于FPGA的高清低碼流H.264攝像機設計

摘要:本文提出了一種基于低成本FPGA的高清低碼流安防攝像機SoC實現方式,該設計已經完全實現,開創了高清低碼流安防攝像機SoC的先河。

本文引用地址:http://www.104case.com/article/247781.htm1. 概述

目前高清H.264攝像機的核心SoC基本上都是ASIC,而FPGA作為近年來發展迅速的可編程器件,在高清H.264攝像機的SoC領域如何能有一席之地?這是我們的設計需要實現的目標。

2. 設計特點

與ASIC相比,FPGA的特點是功能強,設計靈活,隨時升級,工作成果可以積累,NRE低,但是芯片價格比ASIC貴,所以必須找到一個可以達到價格平衡的應用領域,我們根據這幾年智能手機和3G網絡發展迅猛的情況,參考電信運營商第一代全球眼的技術指標,直接把設計指標定位在碼流小于512kbps和分辨率為1280x720x25fps,目前在市面上可以實現這些指標的攝像機幾乎沒有,這是FPGA的好機會。

512kbps的碼流限制主要是考慮到ADSL和家庭光端機的上傳能力,而且也能利用3G上傳視頻,減少了智能手機的碼流下載壓力;1280x720是智能手機的主流分辨率,自然需要相應的視頻源,如果顯示D1或CIF,效果肯定不理想。

我 們的目標是做一個可以直接用于生產的參考設計,除了設計指標先進,我們還要考慮價格和實用,所以我們選擇了低成本的CYCLONE IV系列,另外也實現了一般網絡攝像機的全部功能,如H.264壓縮、720p25幀三碼流、雙向語音、重要區域和隱私區域的定義、智能分析、移動檢測、 聲音偵測、POE供電等;

3. 實現高清低碼流H.264攝像機SoC的關鍵

一般來說,1280×720×25fps的碼流在2Mbps左右,如何降低碼流?除了使用mail profile with cabac的H.264編碼器外,還需要對視頻圖像進行分析,而且要在幀率、分辨率、視頻質量等方面權衡折中,在512kbps碼流下獲得最好的視頻效果,為了達到這樣的目的,需要復雜靈活的控制,FPGA可以滿足這樣的需求。

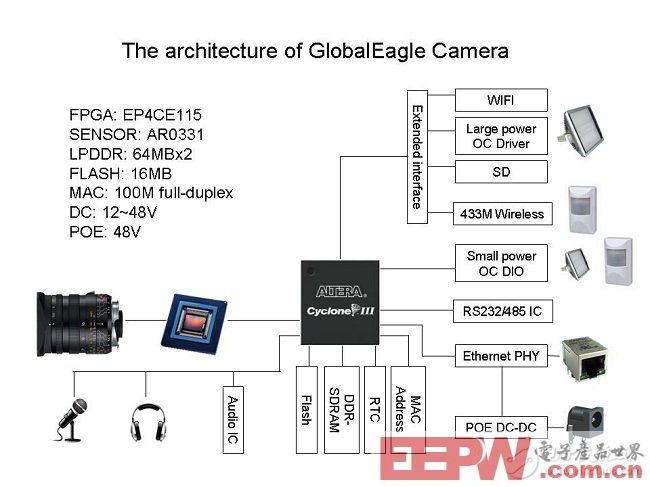

4. 高清低碼流H.264攝像機的結構

高清低碼流H.264攝像機的結構簡圖如下:

圖1 高清低碼流H.264攝像機的結構圖

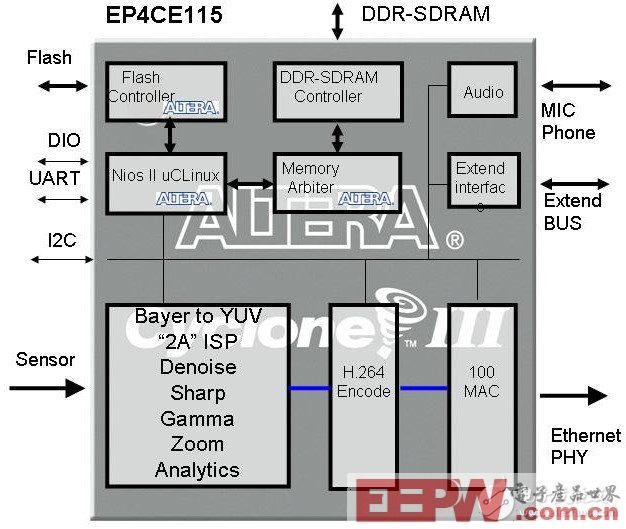

FPGA的內部結構如下圖所示:

圖2 FPGA的內部結構圖

FPGA的選用

在高清低碼流H.264攝像機的結構中,除了圖像傳感器、存儲器、電源和模擬接口外,所有的功能如圖像處理、H.264編碼、協議處理、參數管理、媒體流發送等都由FPGA實現,FPGA就是高清低碼流H.264攝像機的 SoC;目前世界上FPGA的生產商只有幾個,可選擇的產品也不多,要用FPGA實現高清低碼流H.264攝像機的SoC,選擇一款合適的FPGA非常重要,FPGA的選擇主要考慮三方面的因素:速度、成本和結構;每個FPGA生產商都有多個FPGA系列,每個系列的速度、性能和價格都不同,要使高清低碼流H.264攝像機SoC的成本盡可能低,應該選擇成本最低的系列,像我們選擇的FPGA是Altera公司的CYCLONE IV系列,型號是EP4CE115F23C8,CYCLONE IV是低成本系列,在同樣是低成本系列的FPGA中,CYCLONE IV的速度是最快的; FPGA的結構對圖像處理也很重要,尤其是存儲器和乘法器的數量,H.264算法是以宏塊為單位,在處理過程中必然會涉及到宏塊的輸入輸出和緩存,1個宏 塊的數據為384字節(256字節亮度數據和128字節色度數據),如果考慮到輸入輸出和處理的并行,必須設置雙份,即768字節,用CYCLONE IV的1個M9K存儲塊正好,從上面的分析可以看出適合圖像處理的FPGA對內部存儲器的要求是存儲塊容量小(如1KB)、存儲塊數量多,另外,對乘法器的要求也是數量多;在我們選擇FPGA的時候,CYCLONE IV是在所有低成本FPGA中有最大的存儲器邏輯比和乘法器邏輯比,很適合做圖像處理。

圖像傳感器的選擇

為 了滿足1280x720x25fps的要求,只需要選擇百萬像素的傳感器就可以了,我們最終選擇了300萬像素的AR0331,還可以實現 1920x1088x11fps,在實現1280x720x25fps時還有電子PTZ功能,AR0331還有寬動態功能,便于攝像機以后擴充寬動態功 能。

外部存儲器

外部存儲器有2片LP DDR SDRAM和1片串行FLASH,串行FLASH用于存儲FPGA的配置數據和NIOS的數據程序,1片LP DDR SDRAM用于存儲圖像數據和編碼結果,1片LP DDR SDRAM用于NIOSII運行ucLinux。

FPGA實現的功能

FPGA作為高清H.264攝像機的SoC實現的功能如下:

① 圖像處理

● 邊緣檢測RAW插值計算

簡單的RAW插值計算會造成邊緣模糊,增加邊緣檢測判斷可以避免造成邊緣模糊;

● 3D濾波

從圖像傳感器出來的圖像包含有噪聲,去噪同時在幀間和幀內進行;

● 2D銳化

由于鏡頭等因素影響,從圖像傳感器出來的圖像需要銳化才能清晰;

● GAMMA校正

從圖像傳感器出來的圖像灰度不正確,需要做GAMMA校正,獲得正確的灰度;

● 自動曝光控制

根據亮度條件調節適合的曝光參數;

● OSD顯示

可以疊加2048位圖像,圖像以宏塊為單位,結構可以有128x1、64x2、32x4、16x8、8x16、4x32、2x64、1x128等選擇,在屏幕的位置可以設置;

● 區域管理

可以定義隱私區域、運動檢測區域等;

② 編碼處理

● 編碼格式

用H.264 main profile with cabac算法編碼,可以提高壓縮率,減少碼流;由于完全實現H.264的全部算法需要大量的資源,需要很大容量的FPGA,這是不現實的,如我們用1個測試序列做過測試,2個參考幀比1個參考幀的壓縮率提高了5%,但是2個參考幀的處理要比1個參考幀的處理需要多遠不止5%的資源,對于一些很復雜而壓縮 率提高不多的方法我們暫時不采用,降低碼流是1個系統性的工作,需要從多個環節考慮;另外我們必須保證算法的準確,以免在解碼端產生誤差;

● 編碼能力

最大為1280x720x25fps,如果需要同時編碼多路碼流,需要考慮3路碼流的每秒宏塊編碼數量之和不能大于90000,如 1280x720x23fps+320x180x23fps,1136x640x24fps+568x320x24fps+284x160x24fps 等;

● 圖像質量控制

編碼量化參數調整范圍:24~41,值小碼流大,圖像質量好,值大碼流小,圖像質量差;

● 碼流控制

碼流控制方式為CBR,控制平均碼流;

③ 網絡處理

● 網絡速度峰值

目前網絡接口使用全雙工100M以太網,由于圖像的編碼數據量是不均勻的,I幀的編碼數據量大,P幀的編碼數據量小,所以數據量呈脈沖式分布,在傳輸I幀的 編碼數據時盡量采用大的網絡速度有利于減少延遲,但是應該考慮到ADSL的承受能力,可以設置1~70M的網絡速度峰值;

● 碼流均值

碼流均值是1秒種傳送的數據量,可以設置16Kbps~8128Kbps的碼流均值;CBR的碼流控制方式就是根據碼流均值來進行的;

● 碼流緩沖

由于編碼數據量呈脈沖式分布,當編碼的數據產生速度高于網絡速度峰值時,編碼數據就需要緩存在LP DDR SDRAM,否則就會丟失;

● 協議

TCP、RTP、RTSP、DHCP、NTP、HTTP、FTP、SMTP和DDNS;

④ 管理

● NIOS II

NIOS II是內置CPU,運行ucLinux,負責媒體流數據的緩沖和打包發送;

● 參數(通過WEB提供)

接收參數設置和更新,保留2份參數,1份是出廠時的參數,1份是實際使用的參數,在正常加電時實際使用的參數起作用,按復位鍵時出廠時的參數起作用;

● 升級(通過WEB提供)

FLASH里面保存兩個配置數據,1個是出廠時的配置數據,1個是升級后的配置數據,當按復位鍵和升級配置數據加載失敗時按出廠時的配置數據進行加載,否則按升級配置數據加載;

● 報警接口(通過WEB提供)

提供報警信號的上傳功能;

⑤ 音頻

支持雙向64kbits ALaw和16kbits/32kbitsADPCM的收發,聲音偵測。

5. 結束語

用FPGA作為SoC的高清低碼流H.264攝像機已經完成設計,達到設計目標,視頻質量清晰流暢,完全滿足智能手機作為監控終端的要求。

fpga相關文章:fpga是什么

存儲器相關文章:存儲器原理

評論