采用高性能SRAM提高DSP密集型應用的性能

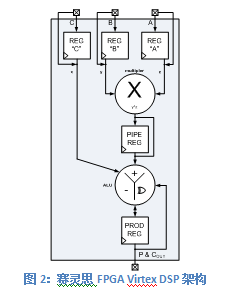

如圖2所示的賽靈思Virtex等FPGA采用專用的DSP塊來高效實現DSP算法。每個DSP塊都包含基于硬件的專用函數,如:乘法、乘法累加、加法、移位、對比、位邏輯函數與模式檢測。通過級聯多個DSP塊可以實現更廣泛的數學函數。

DSP存儲器需求

每個周期執行DSP函數都需要能夠高效地從存儲器提取指令與數據。因此,保持DSP性能的關鍵是高存儲器帶寬。DSP處理器和FPGA DSP塊已經建立了內部高速緩存存儲器架構(L1/L2),以支持每個周期多次的存儲器存取。采用單獨的存儲器組存儲指令與數據,可實現一種超級哈佛架構。處理器采用這種布置能夠在每個周期并行提取指令與數據操作數。另外,DSP算法中的存儲器存取一般呈現出可預測的模式。例如,FIR濾波器系數是按順序循環存取。對于更深的外部存儲,一般采用支持各種SDRAM存儲器(DDR2/3、RLDRAM)、基于硬件的外部存儲器接口(EMIF)。

為了使DSP性能提高兩倍,可以實現采用QDR SRAM完成外部存儲的最新創新性方法。

四倍數據速率(QDR)架構

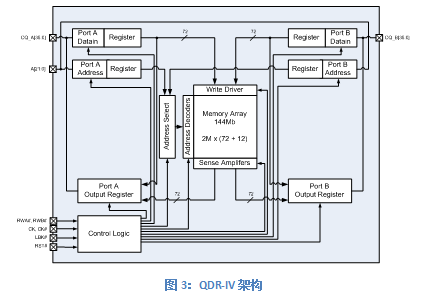

如圖3所示賽普拉斯QDR-IV SRAM等SRAM是針對高吞吐量而精心優化的高性能存儲器器件。此類存儲器具有多個配備雙數據速率(DDR)接口的獨立數據端口。對這些數據端口的存取可同時進行并且相互獨立。地址總線共用,并且根據相關配置以單或雙數據速率運行。目前市場上密度最高的產品為144Mb,而且支持18倍或36倍配置。

QDR-IV SDRAM的架構特點非常有利于需要高吞吐量、低時延和真正隨機存取的數字信號處理流程。

傳統方法(SDRAM)與新方法(QDR-IV)對比

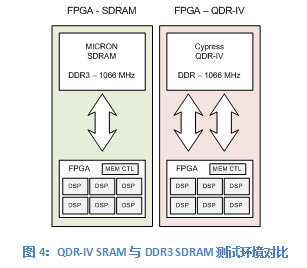

圖4說明了測試環境的整體設置。采用基于FPGA的DSP功能對比不同存儲器類型的最高數據吞吐量。

評論