基于FPGA+DSP的紅外信息數據處理系統設計

現代空戰中,光電對抗裝備在戰爭中扮演著重要的角色,而紅外偵測與跟蹤系統由于采用的無源探測技術,因此與雷達等主動探測系統相比具有隱身性強、抗干擾能力好和小型化程度高等優點,受到業內的關注。新一代紅外成像導引系統須具備高精度、處理速度快、實時性強且反應時間短等特點,這便要求圖像處理計算機能滿足圖像處理中大數據量、復雜運算、實時性強、高傳輸率和穩定可靠等要求。文中從工作原理、硬件及軟件3個方面介紹了基于DSP和FPGA芯片的紅外信息數據處理系統設計方法。

本文引用地址:http://www.104case.com/article/246774.htm1紅外制導控制系統硬件總體設計

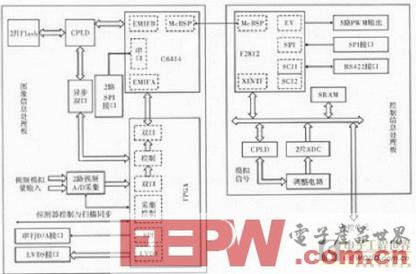

紅外信息數據處理系統按照功能劃分為兩大板塊,由圖像信息處理板和控制信息處理板組成數據處理系統。其紅外制導控制信息數據處理系統如圖1所示。圖像信息處理板主要承擔大量的實時圖像信號預處理、圖像信號處理與控制任務;控制信息處理板控制接口信號的采集,跟蹤回路的解算,控制輸出及與飛控計算機等的通訊,同時控制管理模塊也是系統的管理模塊,完成對系統的輸入/輸出操作、同步控制、系統狀態管理等功能。

圖1 紅外信息數據處理系統框圖

2圖像處理模塊的硬件設計

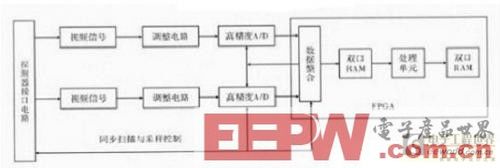

圖像處理模塊的硬件由復位電路、時鐘電路、圖像采集及預處理電路、DSP圖像處理電路、電源轉換電路和外部接口等電路組成。組成框圖如圖2所示。

圖2 圖像采集單元電路組成

2.1圖像采集單元

圖像采集單元包括掃描同步接口電路、探測器接口電路、前端調整電路、A/D轉換電路、采樣控制與數據整合電路及數據緩存(同步雙口)電路等組成。電路組成框圖如圖2所示。掃描同步信號是來自系統中掃描模塊,該信號提供系統時序基準,其信號同步于幀同步信號。掃描同步信號從底板連接器接入。探測器接口電路包括:參考電源、溫度信號、采樣控制信號及2路視頻模擬信號等,以上信號在FPGA內部采集電路的控制下,保證每幀圖像數據的同步采集。調整電路將探測器輸出的視頻信號調整至高速A/D輸入的范圍,差分視頻信號經差分驅動器放大驅動,其共模輸入電壓為視頻A/D片內參考信號(2.5 V)。模擬信號輸入到A/D采用差分輸入方式。視頻A/D主要用于將視頻電路間的模擬信號與數字信號進行轉換。根據電路整體要求,A/D轉換電路需滿足采樣頻率高、功耗低、轉換精度高等要求。采樣控制和數據緩存電路由FPGA內部采樣控制電路完成。數據緩存電路由FPGA內部雙口存儲器完成,具有高速、可同步及異步讀寫操作等性能。

2.2 DSP圖像處理電路

DSP圖像處理電路主要包括處理器及外圍配置電路、存儲器電路及與控制板接口通信的McBSP串口電路等。處理器選用TI公司高性能定點TMS320C641x系列中C6414 GIZA-6E3作為圖像信息處理C6414-6E3,時鐘周期為1.67 ns,內部工作時鐘可達600 MHz,最高處理速度可達4 800 MIPS;內部存儲器容量8 Mbit;有2個擴展存儲器接口,EMIFA為64 bit,EMIFB為16 bit,EMIFA的總線頻率可達133 MHz,最大可尋址空間為1280 MB;內核工作電壓為1.4 V,工作溫度可達-40~105℃。其完成紅外成像制導導引頭圖像組合、分割與增強、模板匹配、背景處理、目標提取和目標跟蹤等主處理算法。

FPGA預處理單元是圖像信息處理板上另一個核心部件,采用Xilinx公司Vertex-II系列中的XC2V2000-FG676來實現。XC2V2000具有200萬門的規模,內部的存儲資源有1 Mbit的Select RAM,336 kbit的Distributed RAM,IO管腳資源達到408個,8個DCM.FPGA預處理單元設計由視頻采集控制與數據整合單元、視頻采集緩沖和主處理緩沖雙口存儲器、預處理單元、圖像輸出子卡數據傳輸接口控制、串行SPI接口控制器、LVDS數字視頻輸出接口、訪問DSP/HPI接口的主機控制電路等部分組成。另外,圖像信息處理板的FPGA配置可實現外場在線配置功能。

存儲器電路包括Flash、FPGA內部同步雙口兩種存儲器。可與C6414的(EMIF外部存儲器接口,C64有2條總線EMIFA與EMIFB)連接,在使用時需通過DSP/BIOS對EMIF總線進行配置,確定訪問時序。圖像信息處理板上有2片Flash資源分別屬于DSP和FPGA,其中屬于FPGA的Flash保存的是板上控制代碼,屬于DSP的Flash除用以存儲模塊BOOT程序,還可對用戶應用程序進行存儲。為了采用從并方式配置FPGA,將其所屬Flash連接在C6414的EMIFB異步BANK CE0,采用異步的讀寫信號;為支持C6414從ROM引導的機制,DSP所屬Flash連接至C6414的EMIFB異步BANK CE1采用異步的讀寫信號。雙口存儲器主要用于存儲幀圖像數據,在圖像信息處理板的FPGA上配置了雙口存儲器。應用中可通過FPGA設計配置同步或異步雙口存儲器與C6414實現數據交換,容量按圖像幀大小可配置為16 kbit×16 bit,也可配置16位或32位訪問方式。圖像信息處理板上雙口存儲器連接在C6414的EMIFA同步BANK ACE0空間,可配置同步方式或異步方式。

fpga相關文章:fpga是什么

評論