一種基于SOPC技術的便攜式定位系統設計

隨著GPS(Global Positioning System)全球定位系統的不斷改進,應用領域正在不斷地開拓,目前已遍及國民經濟各種部門,并開始逐步深入人們的日常生活。當前基于GPS定位產品體積一般較大,且處理核心大多采用單片機,單板機等,產品開發周期長,開發成本高,產品升級不方便,生命周期短。

超大規模集成電路技術的發展,尤其是PLD和FPGA技術的發展,使得在一塊可編程芯片上實現整個的嵌入式系統成為可能。SOPC(System on a programmable chip)技術將CPU,存儲器,I/O接口等系統設計所必須的模塊集成在一片FPGA上,具有設計靈活,可裁減、可擴充、可升級、軟硬件在系統可編程的功能[1]。

本文設計了一種基于SOPC技術的便攜式定位系統,并針對GPS在城市高樓和地下停車場等地方容易出現定位盲區的問題,提出采用GPS/數字指南針組合定位的解決方案。本文首先介紹了系統組成和硬件實現,再對軟件開發作了詳細分析,并給出了源程序,最后對試驗樣機進行了試驗,驗證了系統的可行性。

1 系統基本結構

基于NIOSⅡ的便攜式組合定位系統由兩部分組成:接收終端和監控中心。接收終端接收GPS/數字指南針組合定位信號,并通過GPRS模塊發往監控中心,監控中心將接收到的組合定位信號進行數據融合,采用基于模糊模式識別技術的地圖匹配法,借助GIS電子地圖庫中的高精度道路信息作為分類模板來進行模式識別,根據識別結果來提高GPS接收數據的定位精度,實現數據與電子地圖的實時匹配,實時地顯示接收終端佩戴者所在的位置,授權用戶也可以通過Internet隨時隨地查看終端佩戴者的位置。一旦發生緊急情況,終端佩帶者可以觸發終端上的報警按鈕,由監控中心實時進行相應處理。

2 接收終端硬件設計

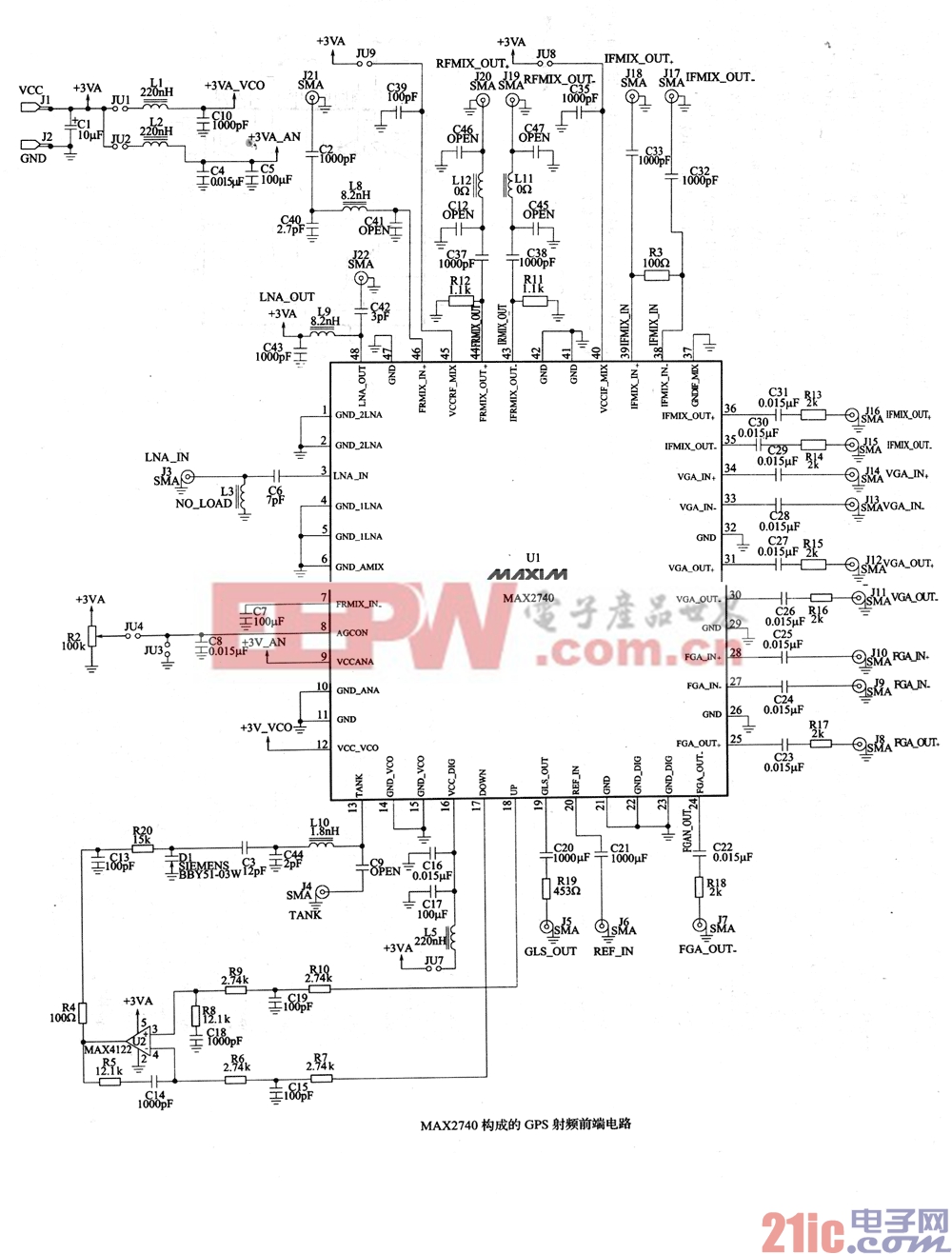

系統接收終端硬件由一塊FPGA芯片和GPS模塊,GPRS模塊,數字指南針模塊,報警模塊等組成,在FPGA芯片中主要實現NIOSⅡ軟核處理器,片上存儲器和數字接口電路的功能。

NIOSⅡ是Altera公司推出的32位RISC嵌入式處理器,能和用戶邏輯相結合,編程至Altera FPGA中。處理器具有32位指令集,32位數據通道和可配置的指令及數據緩沖,實現成本低,在FPGA中實現成本只要35美分,靈活性大,采用軟核形式,具有完全的可定制特性,設計人員可根據實際需求在多種系統設置組合中進行選擇,達到性能、特性和成本最優化,具有超過200DMIP的性能[2]。可以通過下載硬件配置文件到FPGA來實現更新,非常方便。

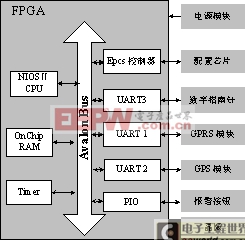

根據系統的功能要求和NIOS II軟核處理器的高度可配置性,在硬件開發工具SOPC Builde定制的NIOS II軟核處理器系統如圖1所示,在一塊Altera EP1C12Q240C8 FPGA上實現了NIOSⅡ軟核CPU,OnChip RAM,Timer,UART,Epcs controller等模塊,NIOSⅡ軟核CPU和其它IP模塊之間通過Avalon片上總線相連,該總線規定了主部件和從部件之間進行連接的端口和通信的時序。

圖1定制的NIOSⅡ處理器系統

UART串口通信模塊用于NIOSⅡ處理器和外部的通信,本系統通過串口采集GPS和數字指南針的定位信號,并通過串口將定位信號和報警信號發給GPRS模塊發往監控中心。On Chip RAM為系統提高片上存儲單元,CY1C12Q240C8提供了239,616 bits的RAM單元,系統無需擴展外部存儲器。Epcs controller模塊用于系統上電時,控制硬件配置文件和程序從串行配置芯片下載到FPGA中。Timer定時器模塊提供系統定時中斷,報警模塊由一個按鈕組成,終端佩帶者遇到緊急情況時通過觸發按鈕向監控中心報警。電源模塊給系統提供系統電源,晶振模塊給系統提供系統時鐘。

評論