基于FPGA的直接數字頻率合成器的設計實現

相位/幅度轉換電路是DDS電路中另一個關鍵,設計中面臨的主要問題就是資源的開銷。電路通常采用ROM結構,相位累加器的輸出是一種數字式鋸齒波,通過取它的高若干位作為ROM的地址輸入,而后通過查表(LUT)和運算后,ROM就輸出所需波形的量化數據。

ROM一般在FPGA(針對Altera公司的器件)中是由EAB實現,并且ROM表的尺寸隨著地址位數或數據位數的增加成指數遞增關系,因此在滿足信號性能的前提條件下,如何減少資源的開銷就是一個重要的問題。在實際設計時我們充分利用了信號周期內的對稱性和算術關系來減少EAB的開銷。

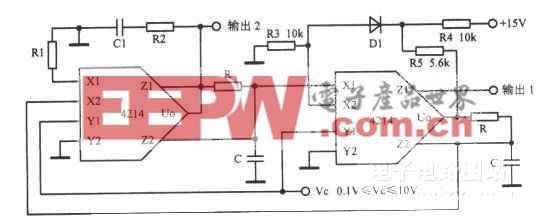

我們利用圖2的結構設計整個DDS電路:

采用Verilog硬件描述語言來實現整個電路,這不僅利于設計文檔的管理,而且方便設計的修改和擴充,以及在不同FPGA器件之間的移植。

由圖2可以清楚地看出整個系統只加入了一級流水線來提高速度,需要說明的是在ROM和系統控制電路之間也可以加入流水線,但實際仿真表明效果不明顯,反而消耗了更多的資源,因此綜合考慮后只加入一級流水線。

為了進一步提高速度,在DDS電路的相位累加器模塊和加法器模塊的設計時并沒有采用FPGA單元庫中的16~32位加法器,盡管它們可以很容易地實現高達32位的相位累加器,但當工作頻率較高時,這種方法不可取,因為它們較大的延時不能滿足速度要求。

因此,具體實現時我們分別用了4個和8個4位的累加器,以流水線的方式實現16位和32位累加器和加法器。比較仿真結果表明,采用流水線技術可以大大提高系統的工作速度。

從前面的分析可知,相位/幅度變換電路也是比較難實現的部分,它不僅要解決速度的問題,還要考慮節省資源的問題。如何有效利用FPGA有限的資源,是實現相位/幅度變換電路的最關鍵一點。

在實際運用中,我們將著眼點主要放在了節省資源上來,相位/幅度轉換電路中的主要問題在于ROM的大小上。由于本次設計的DDS主要用于數字視頻編碼中,因此只需要輸出余弦(正弦)波,我們考慮了以下的優化方式:余弦波信號對于直線成偶對稱,基于此可以將ROM表減至原來的1/2,再利用左半周期內,波形對于點成奇對稱,進一步將ROM表減至最初的1/4,因此通過一個正弦碼表的前1/4周期就可以變換得到正弦和余弦的整個周期碼表。這樣就節省了將近3/4的資源,非常可觀。

系統控制電路主要是根據是否需要相位調制(BPSK)及頻率調制(BFSK),系統時鐘是否需要分頻得到所需的基準時鐘,頻率碼的輸入方式是串行、并行還是微機接口方式,如何控制輸出等具體要求而設計的。這一部分可以靈活設計,凸現FPGA的優點所在。

評論