基于ADSP-BF533的最小系統(tǒng)設(shè)計

l 引 言

ADSP-BF533處理器是Blackfin系列產(chǎn)品的成員,專為滿足當(dāng)今嵌入式音頻、視頻和通信應(yīng)用的計算要求和低功耗條件而設(shè)計的新型16位嵌入式處理器。他基于由ADI和Intel公司聯(lián)合開發(fā)的微信號架構(gòu)(Micro SignalArchitecture,MSA),將一個32位RISC型指令集和雙16位乘法累加(MAC)信號處理功能與通用型微控制器所具有的易用性組合在了一起。ADSP-BF533處理器具有以下主要特點:

(1)最大頻率為600 MHz,1 200 MMACs;

(2)每一個內(nèi)核中帶有2個16位的乘法器,2個40位的累加器,2個40位的邏輯運算單元,4個位的視頻運算單元和1個40位的移位器。在一個指令周期內(nèi)可完成2個16位數(shù)的乘法,2個40位數(shù)的算術(shù)邏輯運算,4個位的視頻數(shù)據(jù)算術(shù)邏輯運算,1個40位的移位運算;

(3)低功耗,采用1.2 V的內(nèi)核電壓和3.3 V的I/O電壓,片內(nèi)集成調(diào)壓器,并且具備動態(tài)電源管理;

(4)高達(dá)148 kB的片內(nèi)存儲器;

(5)豐富的外設(shè)接口,支持與SDRAM,SRAM,F(xiàn)LASH和ROM的無縫連接;

(6)片上JTAG仿真接口。

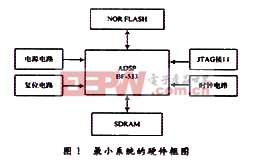

2系統(tǒng)總體設(shè)計

最小系統(tǒng)是由保證處理器可靠工作所必須的基本電路組成的,主要包括電源電路、時鐘電路、復(fù)位電路、SDRAM、FLASH存儲器和JTAG接口電路組成,其硬件框圖如圖1所示。

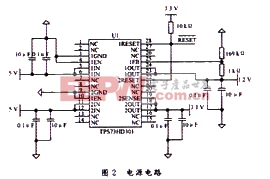

2.1 電源電路

BF-533外部IO供電電壓為3.3 V,內(nèi)核供電電壓為1.2 V。因此,最小系統(tǒng)采用雙電源輸出方案,采用TPS73HD301作為電源芯片,典型輸入電壓為+5 V,輸出電壓為+3.3 V和+1.2 V,每個輸出最大可提供750 mA的電流。TPS73HD301具有電壓監(jiān)控功能,以保證被供電芯片在一個恒壓下正常工作。他為每一路電壓輸出提供一個復(fù)位輸出口,當(dāng)他檢測到輸出的電壓為欠壓狀態(tài)時,與那個輸出電壓相對應(yīng)的RESET管腳將輸出一個低電平,以啟動系統(tǒng)復(fù)位。其電路如圖2所示。

2.2 時鐘電路

BF-533可以使用外部時鐘,也可以使用內(nèi)部振蕩電路。當(dāng)使用外部時鐘時,應(yīng)將此外部時鐘連接到DSP的CLKIN引腳,且XTAL引腳懸空。本系統(tǒng)采用的是內(nèi)部振蕩電路外接晶振的方式,晶振連接到CLKIN和XTAL之間,并與兩個電容相連,如圖3所示。

2.3 復(fù)位電路

手動復(fù)位是最小系統(tǒng)常用的功能,本系統(tǒng)采用專用復(fù)位芯片IMP811實現(xiàn)手動復(fù)位,如圖3所示。

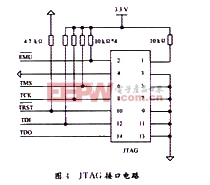

2.4 JTAG接口電路

BF-533提供了一個1EEE 11 49.1 JTAG測試訪問端口。通過此端口,仿真器能夠訪問DSP的內(nèi)部,允許開發(fā)者裝載代碼,設(shè)置斷點,觀察變量和寄存器。本系統(tǒng)采用14針接口的標(biāo)準(zhǔn),如圖4所示。

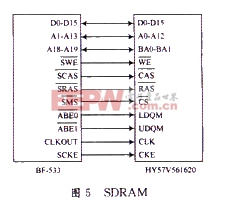

2.5 SDRAM

SDRAM(同步動態(tài)隨機存儲器)具有隨機讀寫速度快,寫入數(shù)據(jù)之前不需要進(jìn)行擦除的特點,在嵌入式系統(tǒng)中成為不可缺少的存儲設(shè)備之一。本系統(tǒng)采用HY57V561620,其容量為32 MB,最高頻率為133 MHz。ADSP-BF533支持與SDRAM的無縫連接,SDRAM的地址映射為OX00000000~OX080000000,其連接方法如圖5所示。

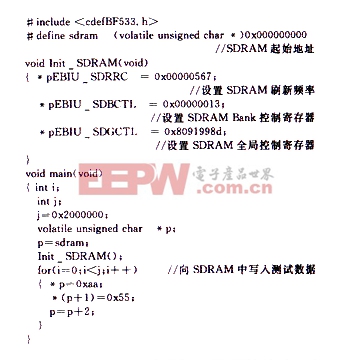

對于SDRAM可以采用以下程序進(jìn)行測試:

該程序?qū)?x2000000個數(shù)寫入SDRAM,在Visual DSP++的BLACKFIN Memory窗口可以觀察到SDRAM的數(shù)據(jù)寫入情況,以驗證寫入是否正確。

2.6 FLASH存儲器

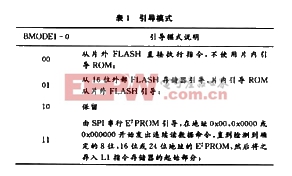

ADSP-BF533具有3種引導(dǎo)模式,如表1所示。當(dāng)上電復(fù)位或者軟件初始化復(fù)位后,處理器采樣復(fù)位配置寄存器BMODE引腳,執(zhí)行引導(dǎo)功能。無論采取何種引導(dǎo)模式,都要從外部存儲器設(shè)備首先讀取一個10個字節(jié)的頭。這個頭指定將被傳輸?shù)淖止?jié)數(shù)量和存儲器的目的地址。多存儲器模塊可被任何引導(dǎo)次序裝載,一但所有模塊被裝載,程序從L1指令SRAM的起始部分開始執(zhí)行指令。

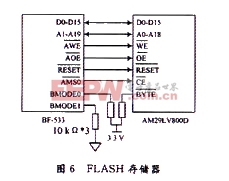

本系統(tǒng)采用NOR FLASH作為引導(dǎo)代碼存儲器,選用容量為1 MB的AM29LV800D,將其接在BF-533異步存儲空間的BANK0上,其地址范圍為0x20000000~0x20100000,電路如圖6所示。

3系統(tǒng)設(shè)計注意事項

(1)對于沒有用到的DSP引腳,應(yīng)將其拉高、拉低,或者定義成輸出端,例如如果nBR,ARDY引腳不用時應(yīng)拉高,RTXI,NMI引腳不用時應(yīng)拉低。

(2)在電路板設(shè)計中,應(yīng)在電源和地之間合理分布去耦電容,以濾除噪聲,提高系統(tǒng)的穩(wěn)定性。

(3)盡量縮短高頻信號的走線,時鐘和負(fù)載的連線盡量短而粗,并且晶振下面不要走線。

4 結(jié) 語

最小系統(tǒng)可以直接作為核心部件應(yīng)用與工程和科研中,具有良好的通用性和可擴展性。在最小系統(tǒng)的基礎(chǔ)上,可以很方便地進(jìn)行二次開發(fā)和功能擴展,能夠縮短開發(fā)周期,降低開發(fā)成本。本文實現(xiàn)了最小系統(tǒng)的基本功能,介紹了各模塊的硬件電路,為DSP應(yīng)用技術(shù)的研究提供了一個良好的平臺。

評論