基于TCPIP協議的高精度多路超聲信號采集系統

摘 要: 針對超聲結構探測應用中回波信號信噪比低且動態范圍大的特性,提出了一種基于分布式總線型結構的多路數據采集系統。該系統以DSP器件為控制核心,配合網絡接口芯片實現了基于TCP/IP協議的節點間通信,同時在信號采集前端采用基于預采樣的自動增益技術,提高了采集精度。通過測試表明,該系統具有良好的性能,具有較高的實用價值。

關鍵詞: DSP;TCP/IP;數據采集

利用超聲波對路橋等建筑進行結構檢測時通常都需要在大空間范圍內進行數據采集,傳統的數據采集方式是將遠端各個傳感器的模擬信號通過電纜引入近端數據采集板卡,由具有多路A/D轉換功能的數據采集板卡進行模數轉換并送入上位機。長距離的傳輸模擬信號容易引入較大的噪聲,降低系統的精度。隨著嵌入式以太網技術的發展,可以將數據采集節點直接放在各個傳感器附近進行數據采集,將轉換完的數字信號通過TCP/IP協議傳入中心控制節點。本文設計了一個基于TCP/IP協議的高精度多路數據采集系統,該系統以TMS320VC5X系列的DSP器件為主控芯片,可以進行大空間范圍的高精度數據采集。另外,超聲回波信號通常具有較大的動態范圍,基于傳統運放的放大技術不能對信號的動態范圍進行限制,這使得A/D轉換的精度降低。本文提出了一種基于預采樣的自動增益電路,可以將輸入信號調整到A/D轉換器的最佳輸入范圍內,提高了A/D轉換的精度。

1 系統總體設計和性能

1.1 系統的總體設計

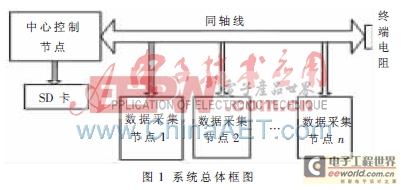

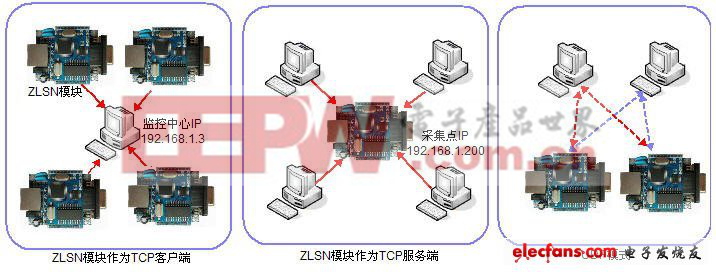

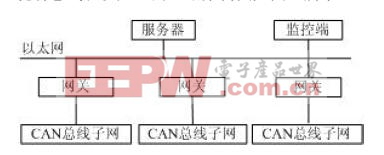

本系統分為中心控制節點和若干數據采集節點。系統的拓撲結構為總線型結構,節點間以TCP/IP協議進行通信。系統開始工作后首先由中心節點以UDP廣播報的形式向所有的數據采集節點發出開始采集命令,數據采集節點接到命令后同步開始數據采集,采集完一個包的數據后按照預定的格式以UDP報的形式將數據發送給中心控制節點。為解決總線型結構通信中常遇到的網絡擁塞問題,本系統將每個數據采集節點所發送的第一個包設計為不同的長度,分支節點1在采集完n1個點后發送,分支節點2在采集完n2個點后發送,…分支節點N在采集完nN個節點后發送。以后的數據包都是等長的,這就分散了網絡的負載,使得發生網絡擁堵的幾率大大降低[3]。中心控制節點負責將接收到的數據保存入SD卡中。系統的總體框圖如圖1所示。

1.2 系統性能指標

根據實際需要,本數據采集系統的技術指標如下:(1)數據采集節點數 1~48道可調;(2)每個通道最大采樣率:大于100 KS/s;(3)采樣精度:24位;(4)道間串擾抑制比:大于70 dB;(5)采集信號動態范圍:120 dB; (6)每通道的最大傳輸速率:10 Mb/s;(7)儀器噪聲:最大15 μV。

2 系統硬件設計

2.1數據采集節點硬件設計

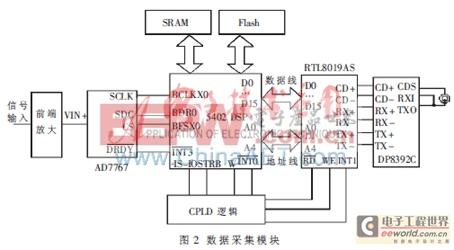

數據采集節點采用TMS320VC5402A DSP芯片作為主控芯片,其最高處理能力可以達到160 MIPS,具有16 K×16 bit的片上RAM,片上配置了3個多通道緩沖串口(可配置為SPI模式),具有快速的中斷響應能力,同時具有多種低功耗模式,這些特性滿足了系統實時性和低功耗的要求,同時其價格相對低廉,有利于降低系統的成本。模數轉換芯片采用24位高精度A/D轉換芯片AD7767,AD7767采用SPI接口,最高采樣頻率可達128 kS/s,在最高工作頻率下的功耗僅為15 mW。網絡通信芯片采用RTL8019AS芯片,將RTL8019AS芯片的AUI接口與同軸電纜驅動芯片DP8392連接,可實現基于10Base2的細同軸電纜通信。數據采集節點的框圖如圖2所示。

2.2 自動增益模塊設計

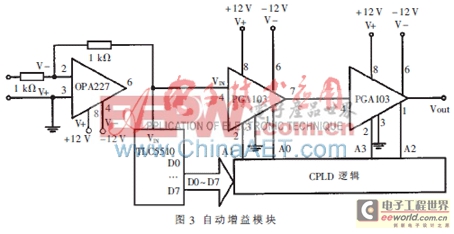

在很多場合下,例如超聲檢測,地質勘探都需要達到很高的采集精度,目前的24位A/D轉換芯片實際上并不能真正的達到24位,同時輸入的模擬信號往往具有很大的動態范圍,不能處于A/D轉換芯片的最佳轉換范圍,因此,本系統采用了基于預采樣和可編程放大器的自動增益電路,以提高系統的轉換精度。前端自動增益模塊的框圖如圖3所示。

要采集的模擬信號首先經過放大倍數為1的高精度運放OPA227,以提高信號的輸入阻抗,減小A/D轉換器對信號的影響。然后將信號送入8位的高速A/D轉換器TLC5510,進行預采樣,將轉換完的結果送入CPLD進行編碼,小信號對應較大的放大階碼,大信號對應較小的放大階碼。用此放大階碼控制可編程增益放大器PGA103,達到自動增益的目的。同時DSP讀取CPLD產生的放大階碼,和AD7767采得的數據一起保存,提高采集的精度。

2.3 中心控制節點的設計

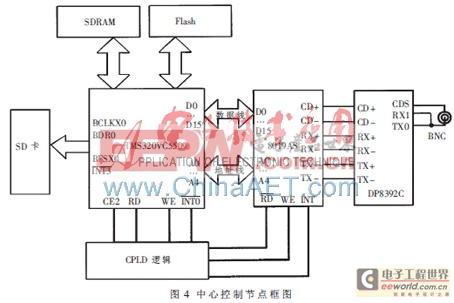

中心控制節點主要實現控制各個數據采集節點、接收采集的數據并保存入SD卡的功能。中心控制節點的設計框圖如圖4所示。

由于中心控制節點要承擔較為繁雜的控制任務,并且要保存較大的數據, 所以它的主控芯片采用TMS320VC5509 ADSP芯片。TMS320VC5509A可以在200 MHz的主頻下穩定工作,具有128 KB的片上RAM,同時可以擴展4 M×16 bit的片外SDRAM,具有支持SD模式和DMA傳輸的SD卡控制器,有利于系統的集成,減小系統的體積。網絡通信接口的設計與數據采集節點相同。

評論