基于CPLD的DSP與聲卡接口技術

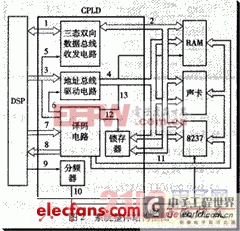

整個系統結構框圖如圖2所示。從圖中可以看出,CPLD主要完成數據總線驅動、地址總線驅動、地址鎖存器、譯碼和時鐘分頻等功能,其中譯碼電路是整個電路的核心。數據總線驅動電路和地址總線驅動將DSP的內部數據與地址總線與外圍電路的數據和地址總線相互隔離;地址鎖存器生成8237在DMA服務周期通過數據線DB0~D7輸出的高8位地址A8~A15。時鐘分頻電路為外電路提供需要的各種頻率的同步時鐘。-譯碼電路為各單元電路以及外圍電路提供讀寫信號、鎖存信號、片選信號和使能信號。

圖2中1為DSP內部系統總線,2為外部數據總線,3為DSP內部地址總線,4為外部地址總線,5為數據總線收發電路使能信號,6為地址總線驅動電路使能信號,7為DSP輸出控制總線,8為CPLD譯碼后輸人DSP的信號線,9為DSP同步外圍電路的時鐘,10為DMA輸人時鐘,11為RAM,8237和聲卡的讀寫信號,12為鎖存信號,13為RAM的片選信號。

3EPM7128S內部譯碼電路的邏輯實現

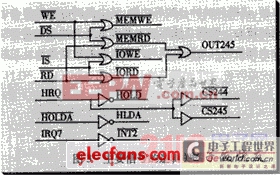

圖3給出了EPM7128S內部譯碼電路主要的輸入和輸出信號以及它們的邏輯關系。其中DSP的地址選通信號和讀寫信號經譯碼分別得到IO讀寫信號和存儲器讀寫信號;8237的DMA申請信號HRQ經反相后送到DSP的HOLD引腳以觸發DSP中斷,DSP在中斷程序里發IDLE指令,HOLDA引腳變為低電子,響應DMA申請;同時數據總線和地址總線驅動電路的使能信號關閉,數據總線和地址總線為高阻態,從而8237可以接管總線,進行DMA操作。聲卡的中斷信號為高電子,須反相后再接DSP的中斷引腳。

4系統工作原理及時序

系統工作的時序如圖4所示。現結合圖2、圖3和圖4將系統工作原理及操作順序說明如下:

(1)聲卡向8237發出DMA請求信號DREQ;

(2)8237通過CPLD向DSP發出HRQ信號;

(3)DSP的HOLD引腳檢測到下降沿后,進入INTl中斷,保護完斷點和現場后,發IDLE指令,DSP的HOLDA引腳電平變低,u向應外部DMA請求;

(4)8237接管總線后,先向聲卡DMA請求的響應信號DACK,表示允許聲卡進行DMA傳送,然后按事先設置的初始地址和需傳送的字節數,依次發送地址和讀寫命令,使得在RAM和聲卡之間直接交換數據,直至全部數據交換完畢;

(5)DMA傳送結束后,自動撤消向CPU的總線請求信號HRQ,此時DSP檢測到麗iS引腳的上升沿,DSP返回到IDLE指令的下一條指令,DSP獲得總線的控制權,繼續在INTl中執行程序。

從上面DSP系統的工作原理可以看出,由于DMA是在中斷程序中完成的,故DSP的DMA執行頻率受限于DSP每秒可執行的中斷次數。

評論